# High Speed, Fast Settling Precision Operational Amplifier

**OP-42**

# **FEATURES**

## **Fast**

| • | Siew Hate              | 50V/μs Min |

|---|------------------------|------------|

| • | Settling-Time (0.01%)  | 1us Max    |

| • | Gain-Bandwidth Product | 10MHz Typ  |

| _ |                        |            |

#### Precise

| • | 100.30                |             |

|---|-----------------------|-------------|

| • | Common-Mode Rejection | 88dB Min    |

| • | Open-Loop Gain        | 500V/mV Min |

| • | Offset Voltage        | 750uV Max   |

|   | Bias Current          | 200pA May   |

# Excellent Radiation Hardness Available in Die Form

# ORDERING INFORMATION †

| T, = 25°0                   | c       |                 | PACK             | AGE         | ,                 | OPERATING            |

|-----------------------------|---------|-----------------|------------------|-------------|-------------------|----------------------|

| V <sub>OS</sub> MAX<br>(mV) |         | CERDIP<br>8-PIN | PLASTIC<br>8-PIN | SO<br>8-PIN | LCC<br>20-CONTACT | TEMPERATURE<br>RANGE |

| 1.0                         | OP42AJ* | OP42AZ*         | _                | _           | OP42ARC/883       | MIL                  |

| 0.75                        | OP42EJ  | OP42EZ          |                  | _           | _                 | IND                  |

| 1.5                         | OP42FJ  | OP42FZ          |                  | _           | _                 | IND                  |

| 5.0                         |         | -               | OP42GP           | OP42GS      | -                 | XIND                 |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- † Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic dip, and TO-can packages.

# **GENERAL DESCRIPTION**

The OP-42 is a fast precision JFET-input operational amplifier. Similar in speed to the OP-17, the OP-42 offers a symmetric

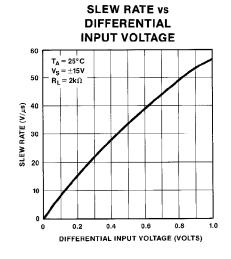

$58V/\mu s$  slew rate and is internally compensated for unity-gain operation. OP-42 speed is achieved with a supply current of less than 6mA. Unity-gain stability, a wide full-power bandwidth of 900kHz, and a fast settling-time of 800ns to 0.01% make the OP-42 an ideal output amplifier for fast digital-to-analog converters.

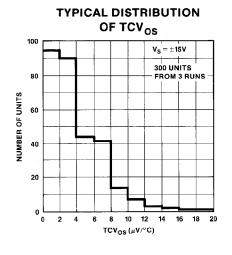

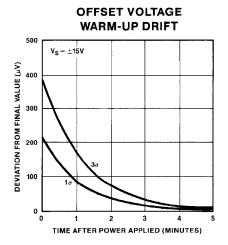

Equal attention was given to both speed and precision in the OP-42 design. Its tight  $750\mu V$  maximum input offset voltage combined with well-controlled drift of less than  $10\mu V/^{\circ}C$  eliminates the need for external nulling in many circuits. The OP-42's

Continued

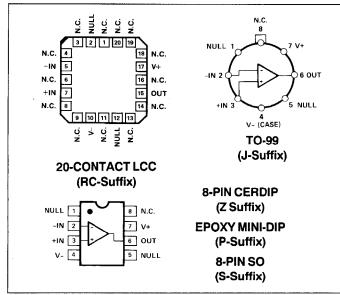

## PIN CONNECTIONS

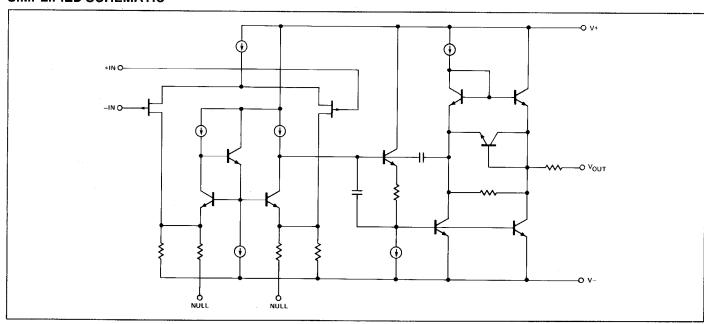

# SIMPLIFIED SCHEMATIC

#### **GENERAL DESCRIPTION Continued**

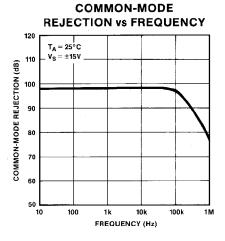

common-mode rejection of 88dB minimum over a  $\pm 11V$  input voltage range is exceptional for a high-speed amplifier. High CMR combined with a minimum 500V/mV gain into  $10k\Omega$  load ensure excellent linearity in both noninverting and inverting gain configurations. The low input bias and offset currents provided by the JFET input stage suit the OP-42 for use in high-speed sample and hold circuits, peak detectors, and log amplifiers. Excellent radiation hardness characteristics make the OP-42 ideal for military and aerospace applications.

The OP-42 conforms to the standard 741 pinout with nulling to V—. The OP-42 upgrades the performance of circuits using the AD544, AD611, AD711, and LF400 by direct replacement. In circuits without nulling, the OP-42 offers an upgrade for designs using the OP-16, OP-17, LT1022, LT1056, and HA2510.

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Supply Voltage                      | ±20V |

|-------------------------------------|------|

| Input Voltage (Note 2)              | ±20V |

| Differential Input Voltage (Note 2) |      |

| Output Short-Circuit Duration       |      |

| Storage Temperature Range          | 65°C to +175°C  |

|------------------------------------|-----------------|

| Operating Temperature Range        |                 |

| OP42A (J, Z)                       | –55°C to +125°C |

| OP42E, F (J, Z)                    | 25°C to +85°C   |

| OP42G                              | 40°C to +85°C   |

| Junction Temperature               | 65°C to +175°C  |

| Lead Temperature Range (Soldering, |                 |

| PACKAGE TYPE           | Θ <sub>jA</sub> (NOTE 3) | Θ <sub>IC</sub> | UNITS |

|------------------------|--------------------------|-----------------|-------|

| TO-99 (J)              | 150                      | 18              | °C/W  |

| 8-Pin Hermetic DIP (Z) | 148                      | 16              | °C/W  |

| 8-Pin Plastic DIP (P)  | 103                      | 43              | °C/W  |

| 20-Contact LCC (RC,TC) | 98                       | 38              | °C/W  |

| 8-Pin SO (S)           | 158                      | 43              | °C/W  |

#### NOTES:

- Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

- 2. For supply voltages less than  $\pm 20V$ , the absolute maximum input voltage is equal to the supply voltage.

- Θ<sub>JA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>JA</sub> is specified for device in socket for TO, CERDIP, P-DIP, and LCC packages; Θ<sub>JA</sub> is specified for device soldered to printed circuit board for SO package.

# **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 15V$ , $T_A = +25$ °C, unless otherwise noted.

|                                  |                  |                                                                                                                                                            | OP-42E            |                   |             | OP-42F            |                   |                        | OP-42G            |                   |     |         |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------|-------------------|-------------------|------------------------|-------------------|-------------------|-----|---------|

| PARAMETER                        | SYMBOL           | CONDITIONS                                                                                                                                                 | MIN               | TYP               | MAX         | MIN               | TYP               | MAX                    | MIN               | TYP               | MAX | UNITS   |

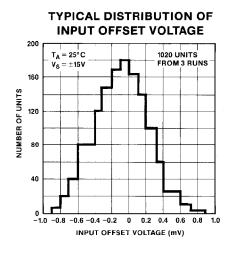

| Offset Voltage                   | v <sub>os</sub>  |                                                                                                                                                            | -                 | 0.3               | 0.75        | _                 | 0.4               | 1.5                    | _                 | 1.5               | 5.0 | mV      |

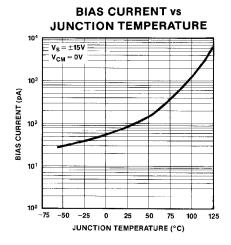

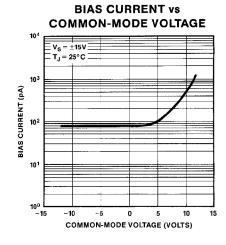

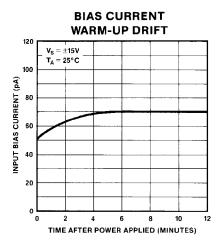

| Input Bias Current               | I <sub>B</sub>   | V <sub>CM</sub> = 0V T <sub>j</sub> = 25°C                                                                                                                 |                   | 80                | 200         |                   | 130               | 250                    | -                 | 130               | 250 | pA      |

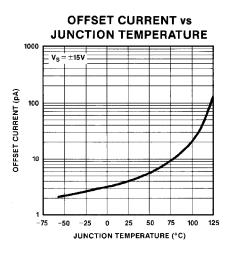

| Input Offset Current             | los              | V <sub>CM</sub> = 0V T <sub>j</sub> = 25°C                                                                                                                 | -                 | 4                 | 40          | _                 | 6                 | 50                     | _                 | 6                 | 50  | pA      |

| Input Voltage Range              | IVR              | (Note 1)                                                                                                                                                   | ±11               | +12.5<br>12.0     | _           | ±11               | +12.5<br>-12.0    | _                      | ±11               | +12.5<br>-12.0    | _   | ٧       |

| Common-Mode<br>Rejection         | CMR              | V <sub>CM</sub> = ±11V                                                                                                                                     | 88                | 98                | -           | 80                | 92                | _                      | 80                | 92                | _   | dB      |

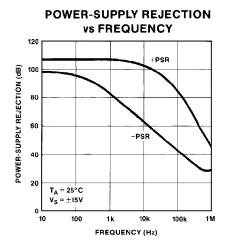

| Power-Supply<br>Rejection Ratio  | PSRR             | V <sub>S</sub> = ±10V<br>to ±20V                                                                                                                           | -                 | 9                 | 40          | -                 | 12                | 50                     | -                 | 12                | 50  | μV/V    |

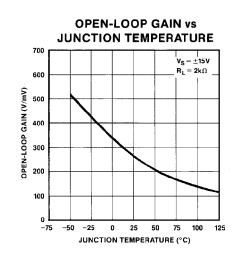

| Large-Signal<br>Voltage Gain     | A <sub>VO</sub>  | $\begin{aligned} R_L &= 10k\Omega \\ R_L &= 2k\Omega \\ R_L &= 1k\Omega \end{aligned}  \begin{aligned} V_0 &= \pm 10V \\ T_j &= 25^{\circ}C \end{aligned}$ | 500<br>200<br>100 | 900<br>260<br>170 | -<br>-<br>- | 500<br>200<br>100 | 900<br>260<br>170 | <del>-</del><br>-<br>- | 500<br>200<br>100 | 900<br>260<br>170 | -   | V/mV    |

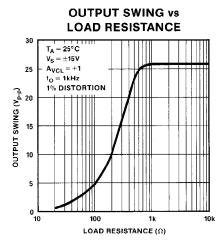

| Output Voltage<br>Swing          | v <sub>o</sub>   | R <sub>L</sub> = 1kΩ                                                                                                                                       | ±11.5             | +12.5<br>-11.9    | _           | ±11.5             | +12.5<br>11.9     | _                      | ±11.5             | +12.5<br>-11.9    | _   | V       |

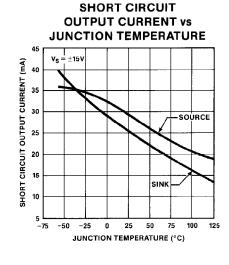

| Short-Circuit<br>Current Limit   | I <sub>sc</sub>  | Output Shorted to Ground                                                                                                                                   | ±20               | +33<br>–28        | ±60         | ±20               | +33<br>–28        | ±60                    | ±20               | +33<br>–28        | ±60 | mA      |

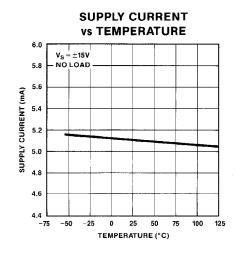

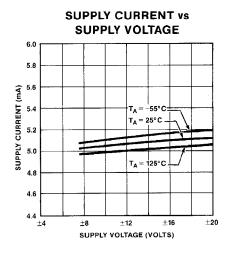

| Supply Current                   | Isy              | No Load<br>V <sub>O</sub> = 0V                                                                                                                             | -                 | 5.1               | 6.0         | -                 | 5.1               | 6.5                    | -                 | 5.1               | 6.5 | mA      |

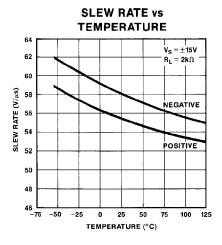

| Slew Rate                        | SR               | - LANAVATO                                                                                                                                                 | 50                | 58                | _           | 40                | 50                | _                      | 40                | 50                | _   | V/μs    |

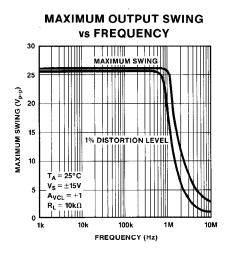

| Full-Power<br>Bandwidth          | вw <sub>р</sub>  | (Note 2)                                                                                                                                                   | 750               | 900               | _           | 600               | 800               | _                      | 600               | 800               | _   | kHz     |

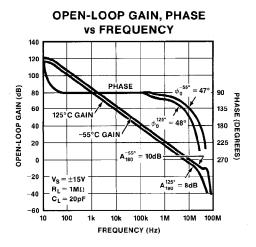

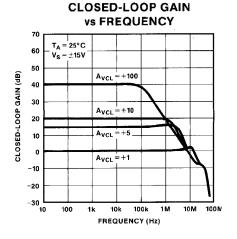

| Gain-Bandwidth<br>Product        | GBW              | f <sub>O</sub> = 10kHz                                                                                                                                     | _                 | 10                | _           | _                 | 10                |                        | _                 | 10                | -   | MHz     |

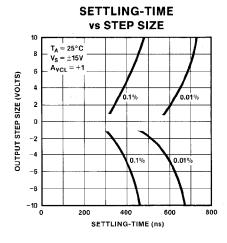

| Settling -Time                   | t <sub>s</sub>   | 10V Step 0.01%<br>(Note 3)                                                                                                                                 | -                 | 0.8               | 1.0         | _                 | 0.9               | 1.2                    | _                 | 0.9               | 1.2 | μs      |

| Overload Recovery<br>Time        | ton              |                                                                                                                                                            | -                 | 700               | _           |                   | 700               |                        | _                 | 700               | _   | ns      |

| Phase Margin                     | φο               | 0db Gain                                                                                                                                                   | _                 | 47                | -           | _                 | 47                | _                      |                   | 47                | _   | degrees |

| Gain Margin                      | A <sub>180</sub> | 180° Open-Loop<br>Phase Shift                                                                                                                              | -                 | 9                 | _           |                   | 9                 | _                      | _                 | 9                 | _   | dB      |

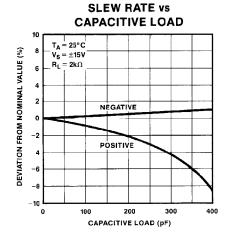

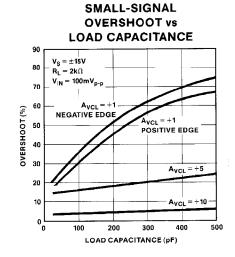

| Capacitive Load Drive Capability | CL               | Unity-Gain Stable<br>(Note 4)                                                                                                                              | 100               | 300               | _           | 100               | 300               | _                      | 100               | 300               | _   | pF      |

# **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 15V$ , $T_A = +25$ °C, unless otherwise noted. *Continued*

|                                        |                    |                         |     | OP-42E               |     |     | OP-42                | =   | OP-42G |                      |     |                   |

|----------------------------------------|--------------------|-------------------------|-----|----------------------|-----|-----|----------------------|-----|--------|----------------------|-----|-------------------|

| PARAMETER                              | SYMBOL             | SYMBOL CONDITIONS       | MIN | TYP                  | MAX | MIN | TYP                  | MAX | MIN    | TYP                  | MAX | UNITS             |

| Differential Input<br>Impedance        | Z <sub>IN</sub>    |                         | -   | 10 <sup>12</sup>   6 | -   | _   | 10 <sup>12</sup>   6 | _   | _      | 10 <sup>12</sup>   6 | -   | Ω[ pF             |

| Open-Loop<br>Output Resistance         | R <sub>O</sub>     |                         | _   | 50                   | _   | _   | 50                   | -   | _      | 50                   | _   | Ω                 |

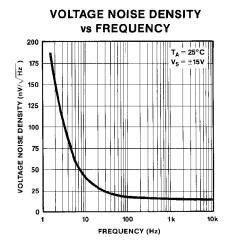

| Voltage Noise                          | e <sub>n p-p</sub> | 0.1Hz to 10Hz           | -   | 2                    | -   |     | 2                    | _   |        | 2                    | _   | μV <sub>p-p</sub> |

|                                        |                    | f <sub>O</sub> = 10Hz   | _   | 38                   |     | _   | 38                   | _   | _      | 38                   | _   |                   |

| Voltage Noise                          | e <sub>n</sub>     | f <sub>O</sub> = 100Hz  | -   | 16                   | _   | _   | 16                   | -   | _      | 16                   | -   | nV/√Hz            |

| Density                                |                    | f <sub>O</sub> = 1kHz   |     | 13                   |     | _   | 13                   | _   | _      | 13                   | -   | HV/√ F1Z          |

|                                        |                    | f <sub>0</sub> = 10kHz  | -   | 12                   | -   |     | 12                   | -   | _      | 12                   | -   |                   |

| Current Noise<br>Density               | in                 | f <sub>O</sub> = 1kHz   | _   | 0.007                |     | _   | 0.007                | _   | _      | 0.007                |     | pA/√Hz            |

| External V <sub>OS</sub><br>Trim Range |                    | R <sub>pot</sub> = 20kΩ | _   | 4                    | _   | -   | 4                    | _   | _      | 4                    | _   | m∨                |

| Long-Term<br>V <sub>OS</sub> Drift     |                    |                         | _   | 5                    | _   | _   | 5                    | _   | -      | 5                    | _   | μV/month          |

| Supply Voltage Range                   | v <sub>s</sub>     |                         | ±8  | ±15                  | ±20 | ±8  | ±15                  | ±20 | ±8     | ±15                  | ±20 | ٧                 |

### NOTES:

# **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 15V$ , $T_A = +25$ °C, unless otherwise noted.

|                                 |                  |                                            |       | OP-42A         |     |         |

|---------------------------------|------------------|--------------------------------------------|-------|----------------|-----|---------|

| PARAMETER                       | SYMBOL           | CONDITIONS                                 | MIN   | TYP            | MAX | UNITS   |

| Offset Voltage                  | Vos              |                                            |       | 0.3            | 1.0 | mV      |

| Input Bias Current              | l <sub>e</sub>   | V <sub>CM</sub> = 0V T <sub>j</sub> = 25°C | _     | 80             | 200 | pΑ      |

| Input Offset Current            | los              | V <sub>CM</sub> = 0V T <sub>j</sub> = 25°C | _     | 4              | 40  | pA      |

| Input Voltage Range             | IVR              | (Note 1)                                   | ±11   | +12.5<br>12.0  | _   | V       |

| Common-Mode<br>Rejection        | CMR              | V <sub>CM</sub> = ±11V                     | 86    | 96             | _   | dB      |

| Power-Supply<br>Rejection Ratio | PSRR             | V <sub>S</sub> = ±10V<br>to ±20V           | _     | 9              | 40  | μV/V    |

| Large-Signal                    |                  | F <sub>1</sub> = 10kΩ V = -10V             | 500   | 900            | _   |         |

| Voltage Gain                    | $A_{VO}$         | $R_1 = 2k\Omega$ $V_0 = 10V$               | 200   | 260            | _   | V/mV    |

|                                 |                  | $R_L = 1k\Omega$ $i = 25 C$                | 100   | 170            | _   |         |

| Output Voltage<br>Swing         | v <sub>o</sub>   | $H_L = 1k\Omega$                           | ±11.5 | +12.5<br>-11.9 | -   | V       |

| Short-Circuit<br>Current Limit  | l <sub>sc</sub>  | Output Shorted<br>to Ground                | ±20   | +33<br>28      | ±60 | mA      |

| Supply Current                  | Isy              | No Load<br>V <sub>O</sub> = 0V             | -     | 5.1            | 6.0 | mA      |

| Slew Rate                       | SR               |                                            | 45    | 52             | _   | V/μs    |

| Full-Power<br>Bandwidth         | BW <sub>p</sub>  | (Note 2)                                   | 700   | 850            | -   | kHz     |

| Gain-Bandwidth<br>Product       | GBW              | f <sub>O</sub> = 10kHz                     | _     | 10             | _   | MHz     |

| Settling -Time                  | t <sub>s</sub>   | 10V Step 0.01%<br>(Note 3)                 | -     | 0.8            | 1.0 | μs      |

| Overload Recovery<br>Time       | t <sub>o n</sub> |                                            | _     | 700            | _   | ns      |

| Phase Margin                    | Фо               | 0db Gain                                   | _     | 47             |     | degrees |

<sup>1.</sup> Guaranteed by CMR test. 2. Guaranteed by slew-rate test and formula  $BW_p = SR/(2\pi 10V_{PEAK})$ .

Settling-time is sample tested for A and E grades. Test circuit is shown in Figure 4. Settling-time for F grade is guaranteed but not tested.

Guaranteed but not tested.

**OP-42 ELECTRICAL CHARACTERISTICS** at  $V_s = \pm 15V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted. *Continued*

|                                        |                    |                                                                                                    |                  | OP-42A               |             |                   |

|----------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|------------------|----------------------|-------------|-------------------|

| PARAMETER                              | SYMBOL             | CONDITIONS                                                                                         | MIN              | TYP                  | MAX         | UNITS             |

| Gain Margin                            | A <sub>180</sub>   | 180° Open-Loop<br>Phase Shift                                                                      | -                | 9                    | _           | dB                |

| Capacitive Load<br>Drive Capability    | CĽ                 | Unity-Gain Stable<br>(Note 4)                                                                      | 100              | 300                  | _           | pF                |

| Differential Input<br>Impedance        | Z <sub>IN</sub>    |                                                                                                    |                  | 10 <sup>12</sup>   6 | _           | Ω  pF             |

| Open-Loop<br>Output Resistance         | R <sub>O</sub>     |                                                                                                    | -                | 50                   | -           | Ω                 |

| Voltage Noise                          | e <sub>n p-p</sub> | 0.1Hz to 10Hz                                                                                      | . –              | 2                    | _           | μV <sub>p-p</sub> |

| Voltage Noise<br>Density               | e <sub>n</sub>     | f <sub>O</sub> = 10Hz<br>f <sub>O</sub> = 100Hz<br>f <sub>O</sub> = 1kHz<br>f <sub>O</sub> = 10kHz | -<br>-<br>-<br>- | 38<br>16<br>13<br>12 | -<br>-<br>- | nV/√Hz            |

| Current Noise<br>Density               | i <sub>n</sub>     | f <sub>O</sub> = 1kHz                                                                              | _                | 0.007                | _           | pA/√Hz            |

| External V <sub>OS</sub><br>Trim Range |                    | R <sub>pot</sub> = 20kΩ                                                                            | -                | 4                    | _           | mV                |

| Long-Term<br>V <sub>OS</sub> Drift     |                    |                                                                                                    | -                | 5                    | _           | μV/month          |

| Supply Voltage Range                   | v <sub>s</sub>     |                                                                                                    | ±8               | ±15                  | ±20         | V                 |

### NOTES:

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $-25^{\circ}C \le T_A \le 85^{\circ}C$  for E/F grades, and  $-40^{\circ}C \le T_A \le +85^{\circ}C$  for G grade, unless otherwise noted.

|                                              |                 |                                                                | OP-42F OP-42F |                | OP-42G |            |                |     |            |                |              |               |

|----------------------------------------------|-----------------|----------------------------------------------------------------|---------------|----------------|--------|------------|----------------|-----|------------|----------------|--------------|---------------|

| PARAMETER                                    | SYMBOL          | CONDITIONS                                                     | MIN           | TYP            | MAX    | MIN        | TYP            | MAX | MIN        | TYP            | MAX          | UNITS         |

| Offset Voltage                               | Vos             |                                                                | _             | 0.4            | 1.2    | _          | 0.6            | 2.5 | -          | 2.0            | 6.0          | mV            |

| Offset Voltage<br>Temperature<br>Coefficient | TCVos           |                                                                | -             | 4              | 10     | _          | 8              |     | -          | 8              | -            | μV/°C         |

| Input Bias Current                           | I <sub>B</sub>  | (Note 1)                                                       | -             | 0.5            | 1.2    | _          | 0.6            | 2.0 | _          | 0.6            | 2.0          | nA            |

| Input Offset Current                         | los             | (Note 1)                                                       | _             | 0.05           | 0.2    |            | 0.06           | 0.4 | _          | 0.06           | 0.4          | nA            |

| Input Voltage Range                          | IVR             | (Note 2)                                                       | ±11           | +12.5<br>-12.0 | _      | ±11        | +12.5<br>-12.0 | _   | ±11        | +12.5<br>-12.0 | <del>-</del> | V             |

| Common-Mode<br>Rejection                     | CMR             | V <sub>CM</sub> = ±11V                                         | 86            | 96             | _      | 80         | 94             | -   | 80         | 94             | _            | dB            |

| Power-Supply<br>Rejection Ratio              | PSRR            | V <sub>S</sub> = ±10V<br>to ±20V                               | _             | 2              | 40     | _          | 6              | 50  | _          | 6              | 50           | μ <b>V/</b> V |

| Large-Signal<br>Voltage Gain                 | A <sub>vo</sub> | $R_L = 10k\Omega$ (Note 1)<br>$R_L = 2k\Omega$ $V_O = \pm 10V$ | 200<br>100    | 500<br>160     | _      | 200<br>100 | 500<br>160     | -   | 200<br>100 | 500<br>160     | _            | V/mV          |

| Output Voltage<br>Swing                      | v <sub>o</sub>  | R <sub>L</sub> = 2kΩ                                           | ±11.0         | +12.3<br>-11.8 | -      | ±11.0      | +12.3<br>-11.8 | _   | ±11.0      | +12.3<br>-11.8 |              | ٧             |

| Short-Circuit<br>Current Limit               | I <sub>sc</sub> | Output Shorted to Ground                                       | ±8            | -              | ±60    | ±8         | _              | ±60 | ±8         | -              | ±60          | mA            |

| Supply Current                               | I <sub>SY</sub> | No Load<br>V <sub>O</sub> = 0V                                 | _             | 5.1            | 6.0    | _          | 5.1            | 6.5 | _          | 5.1            | 6.5          | mA            |

| Slew Rate                                    | SR              | R <sub>L</sub> = 2kΩ                                           | 45            | 57             | -      | 40         | 50             | -   | 40         | 50             | -            | V/µs          |

| Capacitive Load Drive Capability             | CL              | Unity-Gain Stable<br>(Note 3)                                  | 100           | 250            |        | 100        | 250            | -   | 100        | 250            | _            | pF            |

NOTES

<sup>1.</sup> Guaranteed by CMR test.

<sup>2.</sup> Guaranteed by slew-rate test and formula  ${\rm BW}_{\rm p} = {\rm SR}/(2\pi 10 {\rm V}_{\rm PEAK}).$

Settling-time is sample tested for A and E grades. Test circuit is shown in Figure 4. Settling-time for F grade is guaranteed but not tested.

<sup>4.</sup> Guaranteed but not tested.

<sup>1.</sup>  $T_i$  = 85°C for E/F/G Grades;  $T_i$  = 125°C for A grade.

<sup>2.</sup> Guaranteed by CMR test.

<sup>3.</sup> Guaranteed but not tested.

# **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 15V$ , $-55^{\circ}C \le T_A \le 125^{\circ}C$ for A grade, unless otherwise noted.

|                                              |                   |                                                                        |              | OP-42A         |     |       |

|----------------------------------------------|-------------------|------------------------------------------------------------------------|--------------|----------------|-----|-------|

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                             | MIN          | TYP            | MAX | UNITS |

| Offset Voltage                               | V <sub>os</sub>   |                                                                        | _            | 0.5            | 2.0 | mV    |

| Offset Voltage<br>Temperature<br>Coefficient | TCV <sub>os</sub> |                                                                        | _            | 4              | 10  | μV/°C |

| Input Bias Current                           | I <sub>B</sub>    | (Note 1)                                                               | <del>-</del> | 6              | 20  | nA    |

| Input Offset Current                         | los               | (Note 1)                                                               | -            | 0.2            | 1.0 | nA    |

| Input Voltage Range                          | IVR               | (Note 2)                                                               | ±11          | +12.5<br>-12.0 | _   | ٧     |

| Common-Mode<br>Rejection                     | CMR               | V <sub>CM</sub> = ±11V                                                 | 80           | 94             | _   | dB    |

| Power-Supply<br>Rejection Ratio              | PSRR              | V <sub>S</sub> = ±10V<br>to ±20V                                       | -            | 10             | 50  | μV/V  |

| Large-Signal<br>Voltage Gain                 | A <sub>vo</sub>   | R <sub>L</sub> = 10kΩ (Note 1)<br>R <sub>L</sub> = 2kΩ $V_0 = \pm 10V$ | 160<br>80    | 350<br>110     |     | V/mV  |

| Output Voltage<br>Swing                      | v <sub>o</sub>    | R <sub>L</sub> = 2kΩ                                                   | ±11.0        | +12.3<br>-11.8 | _   | ٧     |

| Short-Circuit<br>Current Limit               | <sup>I</sup> sc   | Output Shorted<br>to Ground                                            | ±8           | _              | ±60 | mA    |

| Supply Current                               | Isy               | No Load<br>V <sub>O</sub> = 0V                                         |              | 5.1            | 6.0 | mA    |

| Slew Rate                                    | SR                | R <sub>L</sub> = 2kΩ                                                   | 40           | 52             | -   | V/µs  |

| Capacitive Load Drive Capability             | C <sub>L</sub>    | Unity-Gain Stable<br>(Note 3)                                          | 100          | 250            | _   | pF    |

<sup>1.</sup>  $T_j$  = 85°C for E/F Grades;  $T_j$  = 125°C for A grade. 2. Guaranteed by CMR test.

<sup>3.</sup> Guaranteed but not tested.

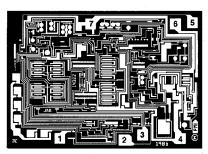

# **DICE CHARACTERISTICS**

DIE SIZE  $0.098 \times 0.070$  inch, 6860 sq. mils (2.49  $\times$  1.78 mm, 4.43 sq. mm)

- 1. OFFSET VOLTAGE NULL

- 2. INVERTING INPUT

- 3. NONINVERTING INPUT

- 4. NEGATIVE SUPPLY

- 5. OFFSET VOLTAGE NULL

- 6. AMPLIFIER OUTPUT

- 7. POSITIVE SUPPLY

# **WAFER TEST LIMITS** at $V_S = \pm 15 V$ , $T_j = 25 ^{\circ} C$ , unless otherwise noted.

| PARAMETER                        | SYMBOL          | CONDITIONS                                                                         | OP-42N<br>LIMIT   | UNITS      |

|----------------------------------|-----------------|------------------------------------------------------------------------------------|-------------------|------------|

|                                  |                 |                                                                                    |                   |            |

| Input Bias Current               | I <sub>B</sub>  | V <sub>CM</sub> = 0V                                                               | 250               | pA MAX     |

| Input Offset Current             | Ios             | V <sub>CM</sub> = 0V                                                               | 50                | pA MAX     |

| Input Voltage Range              | IVR             | (Note 1)                                                                           | ±11               | V MIN      |

| Common-Mode Rejection            | CMR             | $V_{CM} = \pm 11V$                                                                 | 80                | dB MIN     |

| Power-Supply<br>Rejection Ratio  | PSRR            | $V_S = \pm 10V$ to $\pm 20V$                                                       | 50                | μV/V MAX   |

| Large-Signal<br>Voltage Gain     | A <sub>vo</sub> | $egin{aligned} R_L &= 10k\Omega \ R_L &= 2k\Omega \ R_L &= 1k\Omega \end{aligned}$ | 500<br>200<br>100 | V/mV MIN   |

| Output Voltage Swing             | v <sub>o</sub>  | $R_L = 1k\Omega$                                                                   | ±11.5             | V MIN      |

| Short-Circuit<br>Current Limit   | l <sub>sc</sub> | Output Shorted to Ground                                                           | ±20/±60           | mA MIN/MAX |

| Supply Current                   | I <sub>SY</sub> | No Load<br>V <sub>O</sub> = 0V                                                     | 6.5               | mA MAX     |

| Slew Rate                        | SR              |                                                                                    | 40                | V/μs MIN   |

| Capacitive Load Drive Capability | CL              | Unity-Gain Stable<br>(Note 2)                                                      | 100               | pF MIN     |

# NOTES:

- 1. Guaranteed by CMR test.

- 2. Guaranteed but not tested.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dicc. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

# **BURN-IN CIRCUIT**

# TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# TYPICAL PERFORMANCE CHARACTERISTICS

# **APPLICATIONS INFORMATION**

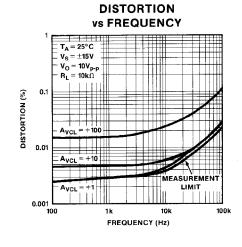

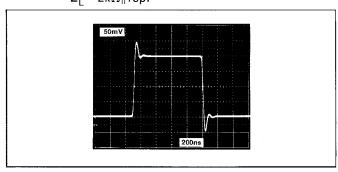

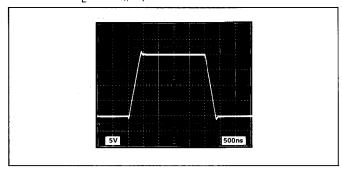

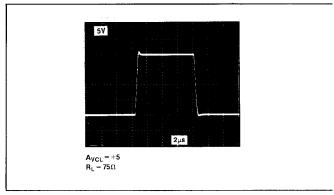

The OP-42 combines speed with a high level of input precision usually found only with slower devices. Well-behaved AC performance in the form of clean transient response, symmetrical slew-rates and a high degree of forgiveness to supply decoupling are the hallmarks of this amplifier. AC gain and phase response are quite independent of temperature or supply voltage. Figure 1 shows the OP-42's small-signal response. Even with 75pF loads, there is minimal ringing in the output waveform. Large-signal response is shown in Figure 2. This figure clearly shows the OP-42's exceptionally close matching between positive and negative slew-rates. Slew-rate symmetry decreases the DC offset a system encounters when processing high-frequency signals, and thus reduces the DC current necessary for load driving.

FIGURE 1: Small-Signal Transient Response,  $Z_1 = 2k\Omega||75pF$

FIGURE 2: Large-Signal Transient Response,  $Z_1 = 2k\Omega || 75pF$

As with most JFET-input amplifiers, the output of the OP-42 may undergo phase inversion if either input exceeds the specified input voltage range. Phase inversion will not damage the amplifier, nor will it cause an internal latch-up.

Supply decoupling should be used to overcome inductance and resistance associated with supply lines to the amplifier.

For most applications a  $0.1\mu$ F to  $0.01\mu$ F capacitor should be placed between each supply pin and ground.

The OP-42 displays excellent resistance to radiation. Radiation hardness data is available by contacting the factory.

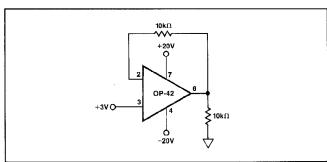

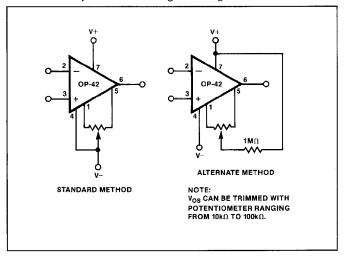

#### **OFFSET VOLTAGE ADJUSTMENT**

Offset voltage is adjusted with a 10k $\Omega$  to 100k $\Omega$  potentiometer as shown in Figure 3. The potentiometer should be connected between pins 1 and 5 with its wiper connected to the V– supply. Nulling V<sub>OS</sub> in this manner changes TCV<sub>OS</sub> by no more than  $5\mu$ V/°C per millivolt of V<sub>OS</sub> change. Alternately, V<sub>OS</sub> may be nulled by attaching the potentiometer wiper through a 1M $\Omega$  resistor to the positive supply rail.

FIGURE 3: Input Offset Voltage Nulling

### **SETTLING-TIME**

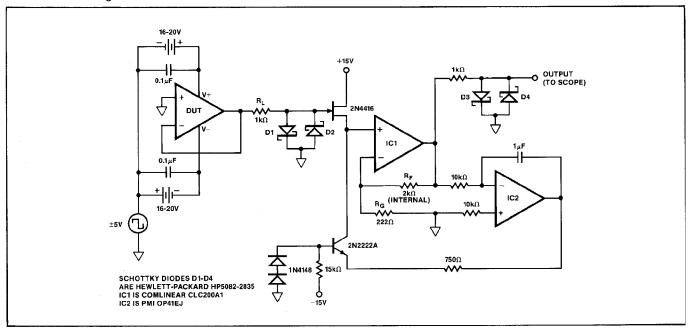

Guaranteed fast-settling is assured by sample-testing during production. The OP-42 is configured as a unity-gain follower in the test circuit of Figure 4. This test method has advantages over false-sum-node techniques in that the actual output of the amplifier is measured, instead of an error-voltage at the sum node. Common-mode settling effects are exercised in this circuit, in addition to the slew-rate and bandwidth effects measured by the false-sum-node method. A reasonably flat-top pulse is required as a stimulus.

The output waveform of the OP-42 being tested is clamped by Schottky diodes and buffered by the JFET source-follower. The signal is amplified by a factor of ten by the fast amplifier IC1, then Schottky-clamped before being output. The OP-41 provides overall offset nulling. Analysis of the waveform using a digitizing oscilloscope determines the op amp's settling-time.

FIGURE 4: Settling-Time Test Fixture

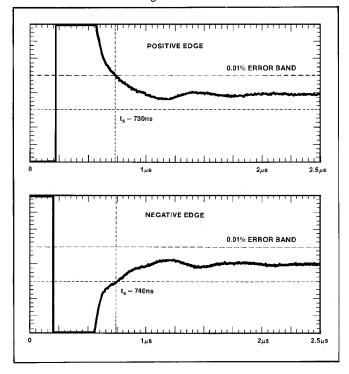

FIGURE 5: OP-42 Settling-Characteristics

# DAC OUTPUT AMPLIFIER

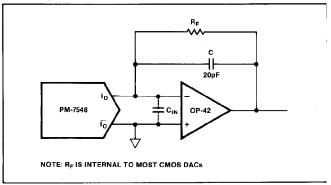

The OP-42 is an excellent choice for a DAC output amplifier, since its high speed and fast settling-time allow quick transitions between codes, even for full-scale changes in output level. The DAC output capacitance appears at the operational amplifier inputs, and must be compensated to ensure

optimal settling speed. Compensation is achieved with capacitor C in Figure 6. C must be adjusted to account for the DAC's output capacitance, the op amp's input capacitance, and any stray capacitance at the inputs. With a bipolar DAC, an additional shunt resistor may be used to optimize response. This technique is described in PMI's application note AN-24.

FIGURE 6: DAC Output Amplifier Circuit

Highest speed is achieved using bipolar DACs such as PMI's DAC-08, DAC-10 or DAC-312. The output capacitances of these converters are up to an order of magnitude lower than their CMOS counterparts, resulting in substantially faster settling-times. The high output impedance of bipolar DACs allows the output amplifier to operate in a true current-to-voltage mode, with a noise gain of unity, thereby retaining the amplifier's full bandwidth. Offset voltage has minimal effect on linearity with bipolar converters.

CMOS digital-to-analog converters have higher output capacitances and lower output resistances than bipolar DACs.

This results in slower settling-times, higher sensitivity to offset voltages and a reduction in the output amplifier's bandwidth. These trade-offs must be balanced against the CMOS DAC's advantages in terms of interfacing capability, power dissipation, accuracy levels and cost. Using the internal feedback resistor which is present on most CMOS converters, the gain applied to offset voltage varies between 4/3 and 2, depending upon output code. Contributions to linearity error will be as much as 2/3V<sub>OS</sub>. In a 10-volt 12-bit system, this may add up to an additional 1/5LSB DNL with the OP-42E. Amplifier bandwidth is reduced by the same gain factor applied to offset voltage, however the OP-42's 10MHz gain-bandwidth product results in no reduction of the CMOS converter's multiplying bandwidth.

Individual DAC data-sheets should be consulted for more complete descriptions of the converters and their circuit applications.

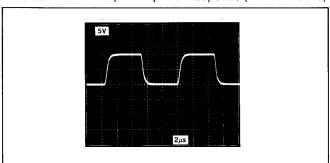

FIGURE 7: DAC Output Amplifier Response (PM-7545 DAC)

# **DRIVING A HIGH-SPEED ADC**

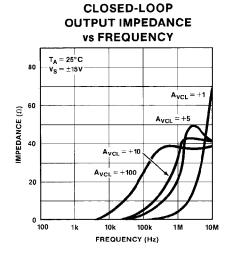

The OP-42's open-loop output resistance is approximately  $50\Omega$ . When feedback is applied around the amplifier, output resistance decreases in proportion to open-loop gain divided by closed-loop gain ( $A_{VOL}/A_{VCL}$ ). Output impedance increases as open-loop gain rolls-off with frequency. High-speed analog-to-digital converters require low source impedances at high frequency. Output impedance at 1MHz is typically  $5\Omega$  for an OP-42 operating at unity-gain. If lower output impedances are required, an output buffer may be placed at the output of the OP-42.

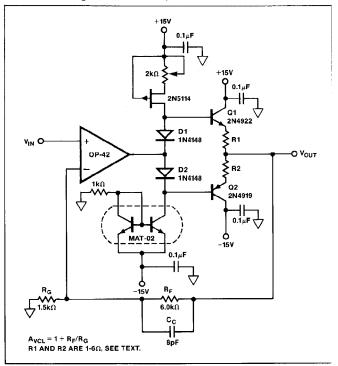

#### **HIGH-CURRENT OUTPUT BUFFER**

The circuit in Figure 8 shows a high-current output stage for the OP-42. Output current is limited by R1 and R2. For good tracking between the output transistors Q1, Q2 and their biasing diodes D1 and D2, thermal contact must be maintained between the transistor and its associated diode. If good thermal contact is not maintained, R1 and R2 must be increased to  $5-6\Omega$  in order to prevent thermal runaway. Using  $5\Omega$  resistors, the circuit easily drives a  $75\Omega$  load (Figure 9). Output resistance is decreased and heavier loads may be driven by decreasing R1 and R2.

Base current and biasing for Q1 and Q2 are provided by two current sources, the MAT-02 and the JFET. The  $2k\Omega$  potentiometer in the JFET current source should be trimmed for optimum transient performance. The case of the MAT-02 should be connected to V–, and decoupled to ground with a

$0.1\mu F$  capacitor. Compensation for the OP-42's input capacitance is provided by  $C_C$ . The circuit may be operated at any gain, in the usual op amp configurations.

FIGURE 8: High-Current Output Buffer

FIGURE 9: Output Buffer Large-Signal Response

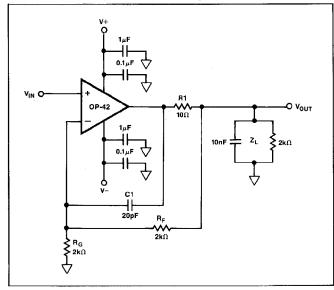

#### **DRIVING CAPACITIVE LOADS**

Best performance will always be achieved by minimizing input and load capacitances around any high-speed amplifier. However, the OP-42 is guaranteed capable of driving a 100pF capacitive load over its full operating temperature range while operating at any gain including unity. Typically, an OP-42 will drive more than 250pF at any temperature. Supply decoupling does affect capacitive load driving ability. Extra care should be given to ensure good decoupling when driving capacitive loads, and a larger decoupling capacitor between  $1\mu F$  and  $10\mu F$  should be placed in parallel with the usual decoupling capacitor on each supply.

Large capacitive loads may be driven utilizing the circuit shown in Figure 10. R1 and C1 introduce a small amount of feedforward compensation around the amplifier to counteract the phase lag induced by the output impedance and load capacitance. At DC and low frequencies, R1 is contained within the feedback loop. At higher frequencies, feedforward compensation becomes increasingly dominant, and R1's effect on output impedance will become more noticeable.

When driving very large capacitances, slew-rate will be limited by the short-circuit current limit. Although the unloaded slew-rate is insensitive to variations in temperature, the output current limit has a negative temperature coefficient, and is asymmetrical with regards to sourcing and sinking current. Therefore, slew-rate into excessive capacities will decrease with increasing temperature, and will lose symmetry.

## **COMPUTER SIMULATIONS**

Many electronic design and analysis programs include models for op amps which calculate AC performance from the location of poles and zeros. As an aid to designers utilizing such a program, major poles and zeros of the OP-42 are listed below. Their location will vary slightly between production lots. Typically, they will be within  $\pm 15\%$  of the frequency listed. Use of this data will enable the designer to evaluate gross circuit performance quickly, but should not supplant rigorous characterization of a breadboarded circuit.

POLES ZEROS 20Hz 1MHz 300kHz 3MHz

FIGURE 10: Compensation for Large Capacitive Loads

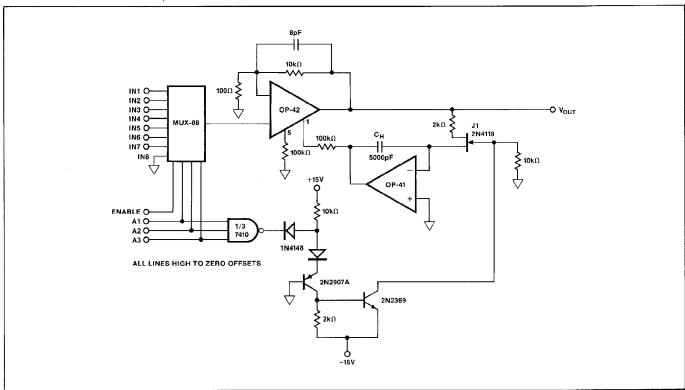

#### **AUTOZEROING OFFSET VOLTAGE**

Figure 11 describes a circuit for automatic offset voltage and drift correction. The OP-41 is used in a servo loop to force the OP-42 output equal to the OP-41's offset voltage. Thus, the OP-42's effective input offset is held below  $10\mu V$  (1mV/A<sub>VCL</sub> = 100) despite any temperature variations. This circuit will be most advantageous in high-gain applications.

Feedback is accomplished using the OP-42's null pins, leaving both inputs free for other purposes. In the application

FIGURE 11: OP-41 Servo Amplifier Provides Offset Correction

shown, the OP-42 has seven multiplexed inputs, while the eighth input provides a ground reference. Nulling is accomplished by addressing the grounded channel. This address should be held for at least  $200\,\mu s$ . After this time, the address may be changed to another channel. The MUX-08 ENABLE pin must be high during the entire nulling cycle. During this time, JFET switch J1 turns on, completing feedback around

the OP-41 servo amplifier. A charge is developed across  $C_H$  to compensate for the OP-42's offset voltage. When another channel is addressed, J1 turns off, and the correction charge is maintained across  $C_H$  by the OP-41. Droop is exceptionally low — only  $1.3 \mu \text{V/s}$  at 25° C. A correction range of more than 4mV allows nulling of minor system offsets as well as the OP-42's offset voltage.