SLVS124F - JUNE 1995 - REVISED JANUARY 1999

- Available in 2.5-V, 3-V, 3.3-V, 4.85-V, and 5-V

Fixed-Output and Adjustable Versions

- Integrated Precision Supply-Voltage Supervisor Monitoring Regulator Output Voltage

- Active-Low Reset Signal with 200-ms Pulse Width

- Very Low Dropout Voltage . . . Maximum of 35 mV at I<sub>O</sub> = 100 mA (TPS7350)

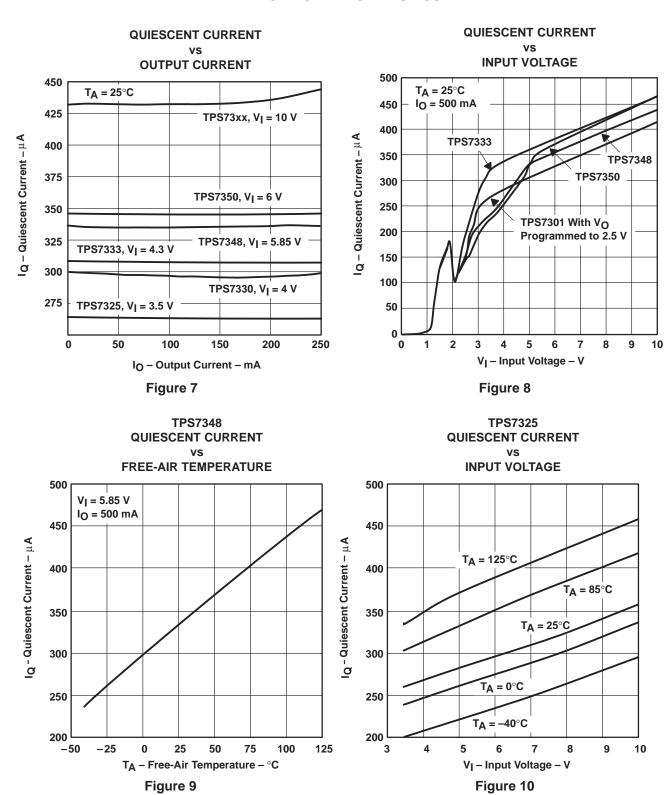

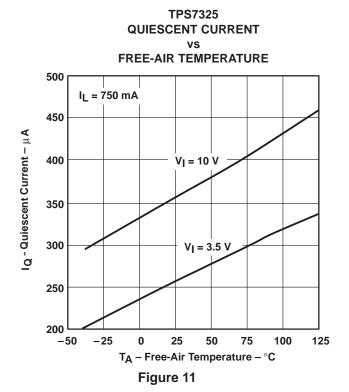

- Low Quiescent Current Independent of Load . . . 340 μA Typ

- Extremely Low Sleep-State Current,

0.5 μA Max

- 2% Tolerance Over Full Range of Load, Line, and Temperature for Fixed-Output Versions§

- Output Current Range of 0 mA to 500 mA

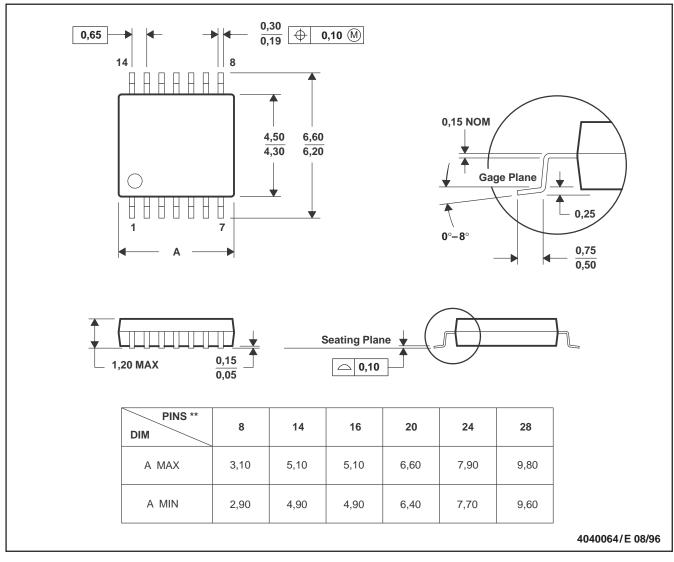

- TSSOP Package Option Offers Reduced Component Height For Critical Applications

### description

The TPS73xx devices are members of a family of micropower low-dropout (LDO) voltage regulators.

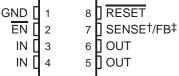

# D OR P PACKAGE (TOP VIEW) D 1 8 RESE

### PW PACKAGE (TOP VIEW)

NC - No internal connection

† SENSE – Fixed voltage options only

(TPS7325, TPS7330, TPS7333, TPS7348, and TPS7350)

‡FB – Adjustable version only (TPS7301)

They are differentiated from the TPS71xx and TPS72xx LDOs by their integrated delayed microprocessor-reset function. If the precision delayed reset is not required, the TPS71xx and TPS72xx should be considered. ¶

#### **AVAILABLE OPTIONS**

| ТЛ       | OUTP  | JT VOL                | TAGE  |       | /E-GOING<br>OLD VOLT |       | Р                       | ACKAGED DEVI       | CES           | CHIP FORM |

|----------|-------|-----------------------|-------|-------|----------------------|-------|-------------------------|--------------------|---------------|-----------|

|          | MIN   | TYP                   | MAX   | MIN   | TYP                  | MAX   | SMALL<br>OUTLINE<br>(D) | PLASTIC DIP<br>(P) | TSSOP<br>(PW) | (Y)       |

|          | 4.9   | 5                     | 5.1   | 4.55  | 4.65                 | 4.75  | TPS7350QD               | TPS7350QP          | TPS7350QPW    | TPS7350Y  |

|          | 4.75  | 4.85                  | 4.95  | 4.5   | 4.6                  | 4.7   | TPS7348QD               | TPS7348QP          | TPS7348QPW    | TPS7348Y  |

| -40°C to | 3.23  | 3.3                   | 3.37  | 2.868 | 2.934                | 3     | TPS7333QD               | TPS7333QP          | TPS7333QPW    | TPS7333Y  |

| 125°C    | 2.94  | 3                     | 3.06  | 2.58  | 2.64                 | 2.7   | TPS7330QD               | TPS7330QP          | TPS7330QPW    | TPS7330Y  |

|          | 2.425 | 2.5                   | 2.575 | 2.23  | 2.32                 | 2.39  | TPS7325QD               | TPS7325QP          | TPS7325QPW    | TPS7325Y  |

|          |       | djustable<br>V to 9.7 |       | 1.101 | 1.123                | 1.145 | TPS7301QD               | TPS7301QP          | TPS7301QPW    | TPS7301Y  |

The D and PW packages are available taped and reeled. Add an R suffix to device type (e.g., TPS7350QDR). The TPS7301Q is programmable using an external resistor divider (see application information). The chip form is tested at 25°C.

The TPS71xx and the TPS72xx are 500-mA and 250-mA output regulators respectively, offering performance similar to that of the TPS73xx but without the delayed-reset function. The TPS72xx devices are further differentiated by availability in 8-pin thin-shrink small-outline packages (TSSOP) for applications requiring minimum package size.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>§</sup> The TPS7325 has a tolerance of  $\pm 3\%$  over the full temperature range.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

### description (continued)

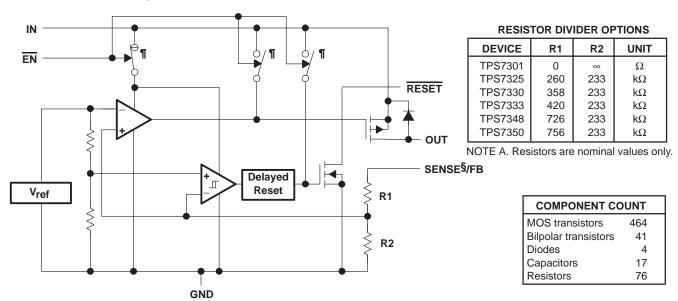

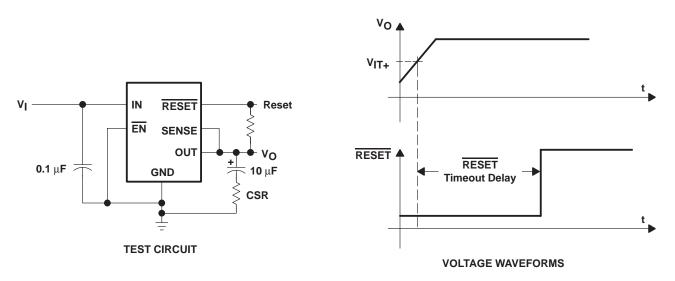

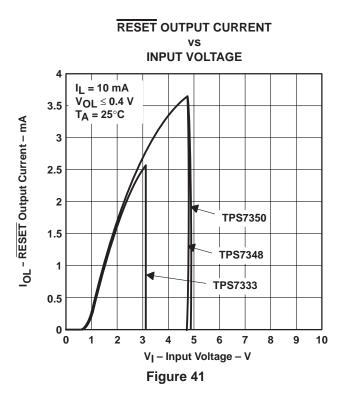

The RESET output of the TPS73xx initiates a reset in microcomputer and microprocessor systems in the event of an undervoltage condition. An internal comparator in the TPS73xx monitors the output voltage of the regulator to detect an undervoltage condition on the regulated output voltage.

If that occurs, the  $\overline{\text{RESET}}$  output (open-drain NMOS) turns on, taking the  $\overline{\text{RESET}}$  signal low.  $\overline{\text{RESET}}$  stays low for the duration of the undervoltage condition. Once the undervoltage condition ceases, a 200-ms (typ) time-out begins. At the completion of the 200-ms delay,  $\overline{\text{RESET}}$  goes high.

An order of magnitude reduction in dropout voltage and quiescent current over conventional LDO performance is achieved by replacing the typical pnp pass transistor with a PMOS device.

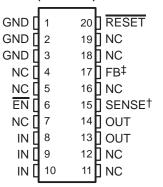

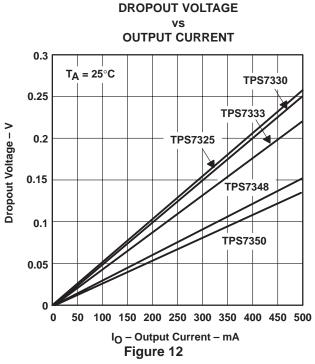

Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (maximum of 35 mV at an output current of 100 mA for the TPS7350) and is directly proportional to the output current (see Figure 1). Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is low and remains constant, independent of output loading (typically 340 µA over the full range of output current, 0 mA to 500 mA). These two key specifications yield a significant improvement in operating life for battery-powered systems.

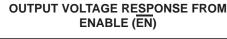

The LDO family also features a sleep mode; applying a logic high signal to  $\overline{EN}$  (enable) shuts down the regulator, reducing the quiescent current to 0.5  $\mu$ A maximum at  $T_J = 25^{\circ}$ C.

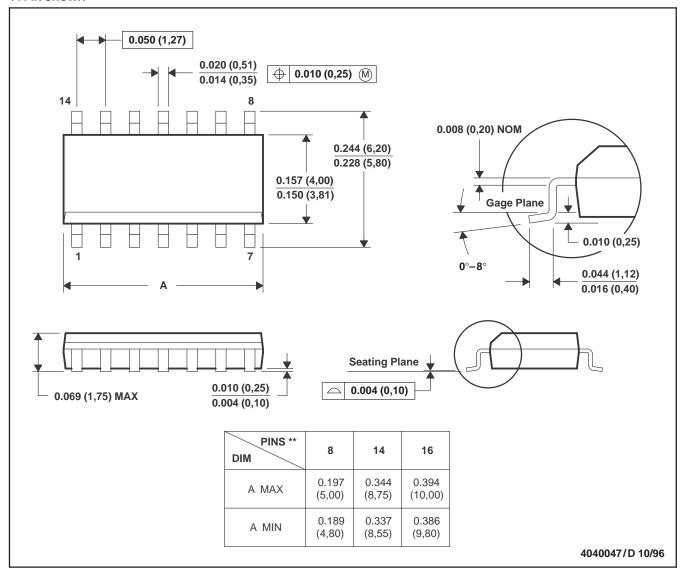

The TPS73xx is offered in 2.5-V, 3-V, 3.3-V, 4.85-V, and 5-V fixed-voltage versions and in an adjustable version (programmable over the range of 1.2 V to 9.75 V). Output voltage tolerance is specified as a maximum of 2% over line, load, and temperature ranges (3% for the 2.5 V and the adjustable version). The TPS73xx family is available in PDIP (8 pin), SO (8 pin) and TSSOP (20 pin) packages. The TSSOP has a maximum height of 1.2 mm.

Figure 1. Dropout Voltage Versus Output Current

† TPS7325, TPS7330, TPS7333, TPS7348, TPS7350 (fixed-voltage options)

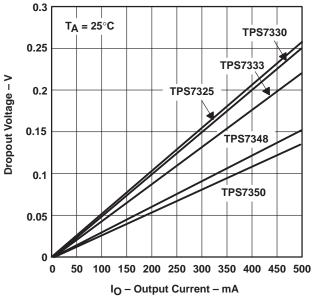

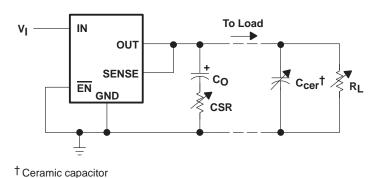

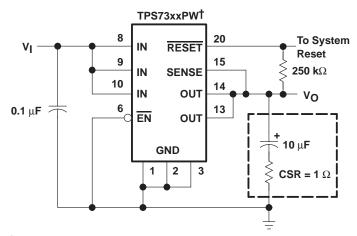

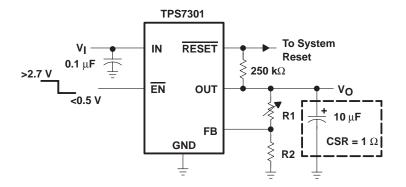

Figure 2. Typical Application Configuration

<sup>‡</sup> Capacitor selection is nontrivial. See application information section for details.

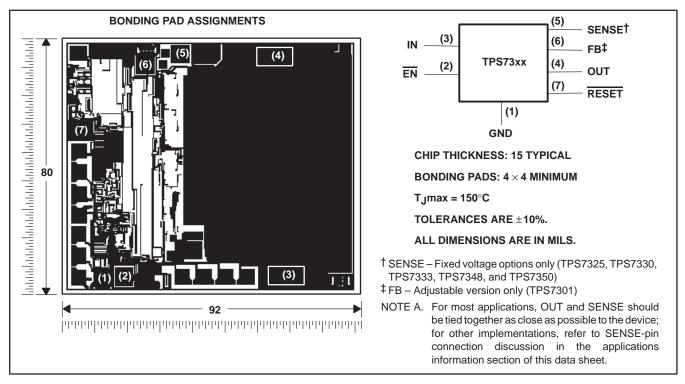

### **TPS73xxY** chip information

These chips, when properly assembled, display characteristics similar to those of the TPS73xxQ. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. Chips may be mounted with conductive epoxy or a gold-silicon preform.

### functional block diagram

<sup>§</sup> For most applications, SENSE should be externally connected to OUT as close as possible to the device. For other implementations, refer to \_SENSE-pin connection discussion in applications information section.

<sup>¶</sup> Switch positions are shown with  $\overline{\mathsf{EN}}$  low (active).

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

### timing diagram

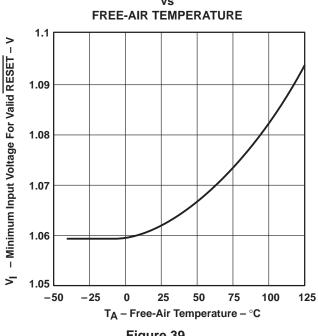

<sup>†</sup> V<sub>res</sub> is the minimum input voltage for a valid RESET. The symbol V<sub>res</sub> is not currently listed within EIA or JEDEC standards for semiconductor symbology.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Input voltage range§, V <sub>I</sub> , RESET, SENSE, EN      | –0.3 V to 11 V                        |

|--------------------------------------------------------------|---------------------------------------|

| Output current, I <sub>O</sub>                               | 2 A                                   |

| Continuous total power dissipation                           | See Dissipation Rating Tables 1 and 2 |

| Operating virtual junction temperature range, T <sub>J</sub> | –55°C to 150°C                        |

| Storage temperature range, T <sub>stg</sub>                  | 65°C to 150°C                         |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                 |

<sup>‡</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>§</sup> All voltage values are with respect to network terminal ground.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

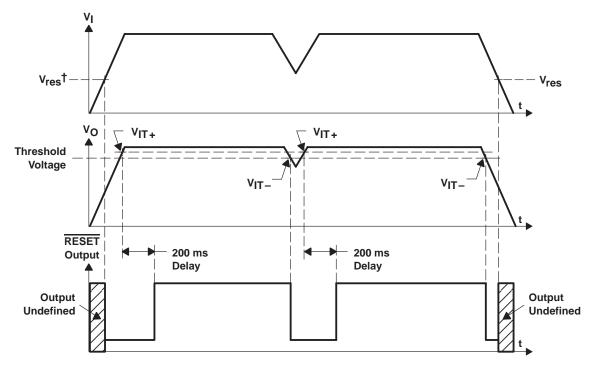

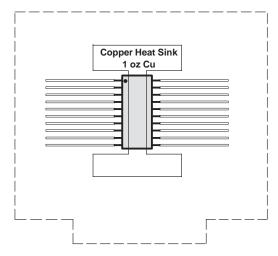

### DISSIPATION RATING TABLE 1 - FREE-AIR TEMPERATURE (SEE FIGURE 3)

| PACKAGE | $T_{\mbox{$\mbox{$A$}}} \leq 25^{\circ}\mbox{$\mbox{$C$}}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|-------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| D       | 725 mW                                                                  | 5.8 mW/°C                                      | 464 mW                                | 145 mW                                 |

| Р       | 1175 mW                                                                 | 9.4 mW/°C                                      | 752 mW                                | 235 mW                                 |

| PW†     | 700 mW                                                                  | 5.6 mW/°C                                      | 448 mW                                | 140 mW                                 |

### DISSIPATION RATING TABLE 2 - CASE TEMPERATURE (SEE FIGURE 4)

| PACKAGE | $T_C \le 25^{\circ}C$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>C</sub> = 25°C | T <sub>C</sub> = 70°C<br>POWER RATING | T <sub>C</sub> = 125°C<br>POWER RATING |

|---------|------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| D       | 2188 mW                            | 9.4 mW/°C                                      | 1765 mW                               | 1248 mW                                |

| Р       | 2738 mW                            | 21.9 mW/°C                                     | 1752 mW                               | 548 mW                                 |

| PWT     | 4025 mW                            | 32.2 mW/°C                                     | 2576 mW                               | 805 mW                                 |

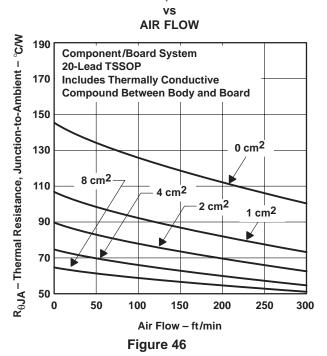

<sup>†</sup> Refer to Thermal Information section for detailed power dissipation considerations when using the TSSOP package.

### MAXIMUM CONTINUOUS DISSIPATION

### VS FREE-AIR TEMPERATURE 1400 $\mathsf{P}_D-\mathsf{Maximum}$ Continuous Dissipation – mW 1200 1000 P Package $R_{\theta JA} = \bar{106}^{\circ}C/W$ 800 D Package 600 $R_{\theta JA} = 172^{\circ}C/W$ 400 PW Package $R_{\theta JA} = 178^{\circ} C/W$ 200 0 25 50 75 100 125 150 $T_A$ – Free-Air Temperature – $^{\circ}C$ Figure 3

### MAXIMUM CONTINUOUS DISSIPATION

Figure 4

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

### recommended operating conditions

|                                 |                   | MIN  | MAX  | UNIT |

|---------------------------------|-------------------|------|------|------|

|                                 | TPS7301Q          | 2.47 | 10   | V    |

| Input voltage, V <sub>1</sub> † | TPS7325Q          | 3.1  | 10   | V    |

|                                 | TPS7330Q          | 3.5  | 10   | V    |

|                                 | TPS7333Q          | 3.77 | 10   |      |

|                                 | TPS7348Q          | 5.2  | 10 V |      |

|                                 | TPS7350Q          | 5.33 | 10   |      |

| High-level input voltage at EN, | √IH               | 2    |      | V    |

| Low-level input voltage at EN,  | /IL               |      | 0.5  | V    |

| Output current range, IO        |                   | 0    | 500  | mA   |

| Operating virtual junction temp | erature range, TJ | -40  | 125  | °C   |

<sup>†</sup> Minimum input voltage defined in the recommended operating conditions is the maximum specified output voltage plus dropout voltage, V<sub>DO</sub>, at the maximum specified load range. Since dropout voltage is a function of output current, the usable range can be extended for lighter loads. To calculate the minimum input voltage for the maximum load current used in a given application, use the following equation:

$$V_{I(min)} = V_{O(max)} + V_{DO(max load)}$$

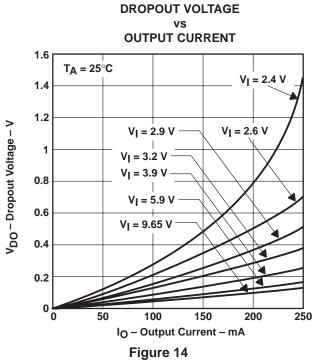

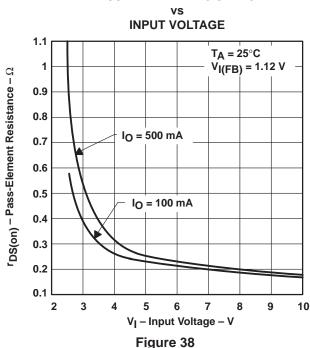

Because the TPS7301 is programmable,  $r_{DS(on)}$  should be used to calculate  $V_{DO}$  before applying the above equation. The equation for calculating  $V_{DO}$  from  $r_{DS(on)}$  is given in Note 2 in the TPS7301 electrical characteristics table. The minimum value of 2.97 V is the absolute lower limit for the recommended input voltage range for the TPS7301.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

# electrical characteristics at I $_{O}$ = 10 mA, $\overline{\text{EN}}$ = 0 V, C $_{o}$ = 4.7 $\mu\text{F}$ (CSR $^{\ddagger}$ = 1 $\Omega$ ), SENSE/FB shorted to OUT (unless otherwise noted)

| PARAMETER                                      | TEST CO                                                  | NDITIONS§                                                | TJ             | MIN  | TYP   | MAX | UNIT   |

|------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------|------|-------|-----|--------|

| Ground current (active mode)                   | <u>EN</u> ≤ 0.5 V,                                       | $V_{I} = V_{O} + 1 V_{r}$                                | 25°C           |      | 340   | 400 |        |

| Ground current (active mode)                   | $0 \text{ mA} \le I_{O} \le 500 \text{ m}$               |                                                          | -40°C to 125°C |      |       | 550 | μΑ     |

| Input current (standby mode)                   | ENL V                                                    | 071/41/401/                                              | 25°C           |      | 0.01  | 0.5 | μА     |

| Imput current (standby mode)                   | $EN = V_I$ ,                                             | $2.7 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V}$ | -40°C to 125°C |      |       | 2   | μΑ     |

| Output current limit                           | V <sub>O</sub> = 0 V,                                    | V <sub>I</sub> = 10 V                                    | 25°C           |      | 1.2   | 2   | Α      |

| Output current innit                           | VO = 0 V,                                                | V  = 10 V                                                | -40°C to 125°C |      |       | 2   | _ ^    |

| Pass-element leakage current in standby        | EN V                                                     | 271/21/2401/                                             | 25°C           |      | 0.01  | 0.5 | μА     |

| mode                                           | $\overline{EN} = V_{I},$                                 | 2.7 V ≤ V <sub>I</sub> ≤ 10 V                            | -40°C to 125°C |      |       | 1   | μΑ     |

| DECET leake as surrent                         | None of an enetice                                       | V at DECET 40 V                                          | 25°C           |      | 0.02  | 0.5 | μΑ     |

| RESET leakage current                          | Normal operation,                                        | V at RESET = 10 V                                        | -40°C to 125°C |      |       | 0.5 | μΑ     |

| Output voltage temperature coefficient         |                                                          |                                                          | -40°C to 125°C |      | 61    | 75  | ppm/°C |

| Thermal shutdown junction temperature          |                                                          |                                                          |                |      | 165   |     | °C     |

| EN la sia biash (atau dhu, ana da)             | 2.5 V ≤ V <sub>I</sub> ≤ 6 V                             |                                                          | -40°C to 125°C | 2    |       |     | V      |

| EN logic high (standby mode)                   | $6 \text{ V} \leq \text{V}_{I} \leq 10 \text{ V}$        |                                                          | -40 C to 125 C | 2.7  |       |     | 1 °    |

| CN legis levy (active made)                    | 2.7 V ≤ V <sub>I</sub> ≤ 10 V                            |                                                          | 25°C           |      |       | 0.5 | V      |

| EN logic low (active mode)                     | $ 2.7 \lor 5 \lor  5 10 \lor$                            |                                                          | -40°C to 125°C |      |       | 0.5 | ı v    |

| EN hysteresis voltage                          |                                                          |                                                          | 25°C           |      | 50    |     | mV     |

| EN 's and some of                              | 0 \ < \ \ < 10 \ \                                       |                                                          | 25°C           | -0.5 | 0.001 | 0.5 |        |

| EN input current                               | $0 \text{ V} \leq \text{V}_{\text{I}} \leq 10 \text{ V}$ |                                                          | -40°C to 125°C | -0.5 |       | 0.5 | μΑ     |

| Minimum V. for active page element             |                                                          |                                                          | 25°C           |      | 2.05  | 2.5 | V      |

| Minimum V <sub>I</sub> for active pass element |                                                          |                                                          | -40°C to 125°C |      |       | 2.5 |        |

| Minimum V. for volid DESET                     | 10 (2000) - 200                                          | A                                                        | 25°C           |      | 1     | 1.5 | V      |

| Minimum V <sub>I</sub> for valid RESET         | IO(RESET) = -300                                         | <i>μ</i> Α                                               | -40°C to 125°C |      |       | 1.9 | l v    |

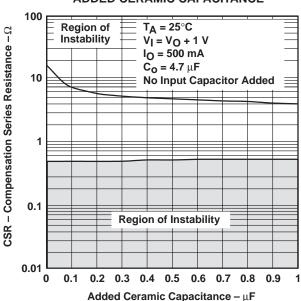

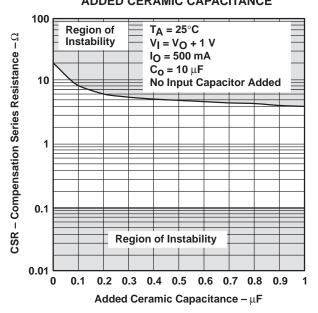

<sup>‡</sup> CSR (compensation series resistance) refers to the total series resistance, including the equivalent series resistance (ESR) of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>0</sub>.

<sup>§</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

## TPS7301Q electrical characteristics at I<sub>O</sub> = 10 mA, V<sub>I</sub> = 3.5 V, $\overline{\text{EN}}$ = 0 V, C<sub>O</sub> = 4.7 $\mu\text{F}$ (CSR<sup>†</sup> = 1 $\Omega$ ), FB shorted to OUT at device leads (unless otherwise noted)

| PARAMETER                                 | TEST CO                                                                | ONDITIONS <sup>‡</sup>                       | TJ             | MIN   | TYP   | MAX                              | UNIT               |  |

|-------------------------------------------|------------------------------------------------------------------------|----------------------------------------------|----------------|-------|-------|----------------------------------|--------------------|--|

|                                           |                                                                        |                                              | 25°C           |       | 1.182 |                                  | V                  |  |

| Reference voltage (measured at FB)        | $2.5 \text{ V} \leq \text{V}_{\text{I}} \leq 10 \text{ V},$ See Note 1 | $5 \text{ mA} \le I_O \le 500 \text{ mA},$   | -40°C to 125°C | 1.147 |       | 1.217                            | V                  |  |

| Reference voltage temperature coefficient |                                                                        |                                              | -40°C to 125°C |       | 61    | 75                               | ppm/°C             |  |

|                                           | V <sub>I</sub> = 2.4 V,                                                | 50 μA ≤ I <sub>O</sub> ≤ 150 mA              | 25°C           |       | 0.7   | 1                                |                    |  |

|                                           | V  = 2.4 V,                                                            | 30 μΑ ≤ 10 ≤ 130 111Α                        | -40°C to 125°C |       |       | 1                                |                    |  |

|                                           | V <sub>I</sub> = 2.4 V,                                                | 150 mA ≤ I <sub>O</sub> ≤ 500 mA             | 25°C           |       | 0.83  | 1.3                              |                    |  |

| Pass-element series resistance            | V  - 2.4 V,                                                            | 130 IIIA 2 IO 2 300 IIIA                     | -40°C to 125°C |       |       | 1.3                              | Ω                  |  |

| (See Note 2)                              | V <sub>I</sub> = 2.9 V,                                                | 50 $\mu$ A ≤ I <sub>O</sub> ≤ 500 mA         | 25°C           |       | 0.52  | 0.85                             | 52                 |  |

|                                           | V  = 2.9 V,                                                            | 30 μΑ ≤ 10 ≤ 300 111Α                        | -40°C to 125°C |       |       | 0.85                             |                    |  |

|                                           | $V_{I} = 3.9 V,$                                                       | $50~\mu\text{A} \leq I_O \leq 500~\text{mA}$ | 25°C           |       | 0.32  |                                  |                    |  |

|                                           | $V_1 = 5.9 V$ ,                                                        | $50~\mu A \leq I_O \leq 500~mA$              | 25°C           |       | 0.23  |                                  |                    |  |

| Input regulation                          | $V_{ } = 2.5 \text{ V to } 10 \text{ V},$                              | 50 $\mu$ A ≤ I <sub>O</sub> ≤ 500 mA,        | 25°C           |       | 3     | 18                               | m\/                |  |

| Imput regulation                          | See Note 1                                                             |                                              | -40°C to 125°C |       |       | 25                               | 111.0              |  |

| Output regulation                         | $2.5 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V},$              | $I_O = 5 \text{ mA to } 500 \text{ mA},$     | 25°C           |       | 5     | 5 14                             | mV                 |  |

|                                           | See Note 1                                                             |                                              | -40°C to 125°C |       |       | 25                               |                    |  |

| Output regulation                         | $2.5 \text{ V} \le \text{V}_{I} \le 10 \text{ V},$                     |                                              | 25°C           |       | 7     | 22                               | mV                 |  |

|                                           | See Note 1                                                             |                                              | -40°C to 125°C |       |       | 54                               |                    |  |

|                                           |                                                                        | I <sub>O</sub> = 50 μA                       | 25°C           | 48    | 59    |                                  |                    |  |

| Ripple rejection                          | f = 120 Hz                                                             | ΙΟ = 30 μΑ                                   | -40°C to 125°C | 44    |       | 3 18 mV 25 14 mV 25 7 22 mV 9 dB |                    |  |

| Kipple rejection                          | 1 = 120112                                                             | I <sub>O</sub> = 500 mA,                     | 25°C           | 45    | 54    |                                  | l ub               |  |

|                                           |                                                                        | See Note 1                                   | -40°C to 125°C | 44    |       |                                  |                    |  |

| Output noise-spectral density             | f = 120 Hz                                                             |                                              | 25°C           |       | 2     |                                  | μV/√ <del>Hz</del> |  |

|                                           |                                                                        | $C_0 = 4.7  \mu F$                           | 25°C           |       | 95    |                                  |                    |  |

| Output noise voltage                      | 10 Hz ≤ f ≤ 100 kHz                                                    | C <sub>O</sub> = 10 μF                       | 25°C           |       | 89    |                                  | μVrms              |  |

|                                           |                                                                        | C <sub>O</sub> = 100 μF                      | 25°C           |       | 74    |                                  |                    |  |

| RESET trip-threshold voltage§             | VO(FB) decreasing                                                      | -                                            | -40°C to 125°C | 1.101 |       | 1.145                            | V                  |  |

| RESET hysteresis voltage§                 | Measured at VO(FB)                                                     |                                              | 25°C           |       | 12    |                                  | mV                 |  |

| DEGET autout laurante au 8                | Ì                                                                      | 1 400 4                                      | 25°C           |       | 0.1   | 0.4                              | .,                 |  |

| RESET output low voltage§                 | V <sub>I</sub> = 2.13 V,                                               | $IO(RESET) = 400 \mu A$                      | -40°C to 125°C |       |       | 0.4                              | V                  |  |

| ED input ourrent                          |                                                                        |                                              | 25°C           | -10   | 0.1   | 10                               | - ^                |  |

| FB input current                          |                                                                        |                                              | -40°C to 125°C | -20   |       | 20                               | nA                 |  |

<sup>†</sup> CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>0</sub>.

NOTES: 1. When V<sub>I</sub> < 2.9 V and I<sub>O</sub> > 150 mA simultaneously, pass element r<sub>DS(on)</sub> increases (see Figure 33) to a point where the resulting dropout voltage prevents the regulator from maintaining the specified tolerance range.

2. To calculate dropout voltage, use equation: VDO = IO · rDS(on) rDS(on) is a function of both output current and input voltage. This parametric table lists rDS(on) for VI = 2.4 V, 2.9 V, 3.9 V, and 5.9 V, which corresponds to dropout conditions for programmed output voltages of 2.5 V, 3 V, 4 V, and 6 V respectively. For other programmed values, refer to Figure 33.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

<sup>§</sup> Output voltage programmed to 2.5 V with closed-loop configuration (see application information).

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

# TPS7325Q electrical characteristics at I $_{O}$ = 10 mA, V $_{I}$ = 3.5 V, $\overline{EN}$ = 0 V, C $_{o}$ = 10 $\mu F$ (CSR $^{\dagger}$ = 1 $\Omega$ ), SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                        | TEST CO                                                   | NDITIONS <sup>‡</sup>                              | TJ             | MIN   | TYP  | MAX   | UNIT   |

|----------------------------------|-----------------------------------------------------------|----------------------------------------------------|----------------|-------|------|-------|--------|

| Output voltage                   |                                                           |                                                    | 25°C           | 2.45  | 2.5  | 2.55  | V      |

| Output voltage                   | $3.5 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V},$ | $5~\text{mA} \leq I_{\mbox{O}} \leq 500~\text{mA}$ | -40°C to 125°C | 2.425 |      | 2.575 | V      |

|                                  | IO = 10 mA,                                               | V <sub>I</sub> = 2.97 V                            | 25°C           |       | 5    |       |        |

|                                  | 10 = 10 mA,                                               | V  = 2.97 V                                        | -40°C to 125°C |       |      | 14    |        |

| Dropout voltage§                 | I <sub>O</sub> = 100 mA,                                  | V <sub>I</sub> = 2.97 V                            | 25°C           |       | 50   | 80    | mV     |

| Dropout voltages                 | 10 = 100 mz,                                              | V   - 2.57 V                                       | -40°C to 125°C |       |      | 150   | ] '''  |

|                                  | IO = 500 mA,                                              | V <sub>I</sub> = 2.97 V                            | 25°C           |       | 270  | 400   |        |

|                                  | 10 = 300 IIIA,                                            | V  = 2.97 V                                        | -40°C to 125°C |       |      | 600   |        |

| Pass-element series resistance§  | (2.97 V – V <sub>O</sub> )/I <sub>O</sub> ,               | V <sub>I</sub> = 2.97 V,                           | 25°C           |       | 0.5  | 0.7   | Ω      |

| r ass-element series resistances | I <sub>O</sub> = 500 mA                                   |                                                    | -40°C to 125°C |       |      | 1.4   | 52     |

| nput regulation                  | V <sub>I</sub> = 3.5 V to 10 V,                           | 50 μA ≤ I <sub>O</sub> ≤ 500 mA                    | 25°C           |       | 6    | 20    | mV     |

| input regulation                 | V = 3.5 V to 10 V,                                        | 30 μΑ ≤ 10 ≤ 300 πΑ                                | -40°C to 125°C |       |      | 25    | IIIV   |

| Output regulation                | I <sub>O</sub> = 5 mA to 500 mA,                          | 35 V < V, < 10 V                                   | 25°C           |       | 20   | 32    | mV     |

|                                  | 10 = 3 mA to 300 mA,                                      | 3.5 V \( \( \) \( \) \( \)                         | -40°C to 125°C |       |      | 50    | IIIV   |

| Output regulation                | $I_{O} = 50 \mu\text{A} \text{ to } 500 \text{mA},$       | 35 V < V1 < 10 V                                   | 25°C           |       | 28   | 60    | mV     |

|                                  | 10 = 30 μλ 10 300 πλ,                                     | 3.5 V 2 V 2 10 V                                   | -40°C to 125°C | 28 60 | IIIV |       |        |

|                                  |                                                           | ΙΟ = 50 μΑ                                         | 25°C           | 50    | 53   |       |        |

| Ripple rejection                 | f = 120 Hz                                                | ΙΟ = 30 μΑ                                         | -40°C to 125°C | 49    |      |       | dB     |

| Kippie rejection                 | 1 = 120112                                                | 10 - 500 mA                                        | 25°C           | 49    | 53   |       | ub     |

|                                  |                                                           | I <sub>O</sub> = 500 mA                            | -40°C to 125°C | 32    |      |       |        |

| Output noise-spectral density    | f = 120 Hz                                                |                                                    | 25°C           |       | 2    |       | μV/√Hz |

|                                  |                                                           | $C_0 = 4.7  \mu F$                                 | 25°C           |       | 274  |       |        |

| Output noise voltage             | 10 Hz ≤ f ≤ 100 kHz                                       | C <sub>O</sub> = 10 μF                             | 25°C           |       | 228  |       | μVrms  |

|                                  |                                                           | C <sub>O</sub> = 100 μF                            | 25°C           |       | 159  |       |        |

| RESET trip-threshold voltage     | V <sub>O</sub> decreasing                                 | •                                                  | -40°C to 125°C | 2.23  | 2.32 | 2.39  | V      |

|                                  | V 04V                                                     |                                                    | 25°C           |       | 0.14 | 0.4   |        |

| RESET output low voltage         | V <sub>I</sub> = 2.1 V,                                   | IO(RESET) = -0.8  mA                               | -40°C to 125°C |       |      | 0.4   | V      |

TCSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to Co.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

<sup>§</sup> Dropout test and pass-element series resistance test are not production tested. Test method requires SENSE terminal to be disconnected from output voltage.

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

# TPS7330Q electrical characteristics at I $_{O}$ = 10 mA, V $_{I}$ = 4 V, $\overline{EN}$ = 0 V, C $_{O}$ = 4.7 $\mu\text{F}$ (CSR $^{\dagger}$ = 1 $\Omega$ ), SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                      | TEST CO                                             | NDITIONS <sup>‡</sup>                     | TJ             | MIN  | TYP  | MAX  | UNIT               |

|--------------------------------|-----------------------------------------------------|-------------------------------------------|----------------|------|------|------|--------------------|

| Custout valtage                |                                                     |                                           | 25°C           |      | 3    |      | V                  |

| Output voltage                 | $4 \text{ V} \le V_{I} \le 10 \text{ V},$           | $5 \text{ mA} \le I_O \le 500 \text{ mA}$ | -40°C to 125°C | 2.94 |      | 3.06 | V                  |

|                                | IO = 10 mA,                                         | V <sub>I</sub> = 2.94 V                   | 25°C           |      | 5.2  | 7    |                    |

|                                | IO = 10 IIIA,                                       | V  = 2.94 V                               | -40°C to 125°C |      |      | 10   |                    |

| Dropout voltage                | I <sub>O</sub> = 100 mA,                            | V <sub>I</sub> = 2.94 V                   | 25°C           |      | 52   | 75   | mV                 |

| Dropout voltage                | 10 = 100 mz,                                        | V   = 2.94 V                              | -40°C to 125°C |      |      | 100  | ] '''              |

|                                | IO = 500 mA,                                        | V <sub>I</sub> = 2.94 V                   | 25°C           |      | 267  | 450  |                    |

|                                | 10 = 300 mA,                                        | V  = 2.94 V                               | -40°C to 125°C |      |      | 500  |                    |

| Pass-element series resistance | (2.94 V – V <sub>O</sub> )/I <sub>O</sub> ,         | V <sub>I</sub> = 2.94 V,                  | 25°C           |      | 0.5  | 0.7  | Ω                  |

| Fass-element series resistance | $I_{O} = 500 \text{ mA}$                            |                                           | -40°C to 125°C |      |      | 1    | 22                 |

| Input regulation               | V <sub>I</sub> = 4 V to 10 V,                       | 50 μA ≤ I <sub>O</sub> ≤ 500 mA           | 25°C           |      | 6    | 6 23 | mV                 |

| Input regulation               | V = 4 V 10 10 V,                                    | 20 ha ≥ 10 ≥ 200 ma                       | -40°C to 125°C |      |      | 29   | IIIV               |

| Output regulation              | I <sub>O</sub> = 5 mA to 500 mA,                    | 4 V < V < 10 V                            | 25°C           |      | 20   | 32   | mV                 |

|                                | 10 = 3 mA to 300 mA,                                | 4 V \( \times V \( \) \( \) \( \)         | -40°C to 125°C |      |      | 60   | IIIV               |

| Output regulation              | $I_{O} = 50 \mu\text{A} \text{ to } 500 \text{mA},$ | 4 V < V1 < 10 V                           | 25°C           |      | 28   | 60   | mV                 |

|                                | $10 = 30 \mu\text{A to } 300 \text{mA},$            | 4 0 2 0 2 10 0                            | -40°C to 125°C |      |      | 120  | IIIV               |

|                                |                                                     | ΙΟ = 50 μΑ                                | 25°C           | 43   | 53   |      |                    |

| Ripple rejection               | f = 120 Hz                                          | ΙΟ = 50 μΑ                                | -40°C to 125°C | 40   |      |      | dB                 |

| Ripple rejection               | T = 120 HZ                                          | 10 - 500 mA                               | 25°C           | 39   | 53   |      | uБ                 |

|                                |                                                     | I <sub>O</sub> = 500 mA                   | -40°C to 125°C | 36   |      |      |                    |

| Output noise-spectral density  | f = 120 Hz                                          |                                           | 25°C           |      | 2    |      | μV/√ <del>Hz</del> |

|                                |                                                     | $C_0 = 4.7  \mu F$                        | 25°C           |      | 274  |      |                    |

| Output noise voltage           | 10 Hz ≤ f ≤ 100 kHz                                 | C <sub>O</sub> = 10 μF                    | 25°C           |      | 228  |      | μVrms              |

|                                |                                                     | C <sub>O</sub> = 100 μF                   | 25°C           |      | 159  |      |                    |

| RESET trip-threshold voltage   | V <sub>O</sub> decreasing                           |                                           | -40°C to 125°C | 2.58 | 2.64 | 2.7  | V                  |

| DEOET autout laws alto as      | V 00V                                               |                                           | 25°C           |      | 0.14 | 0.4  | .,                 |

| RESET output low voltage       | V <sub>I</sub> = 2.6 V,                             | IO(RESET) = -0.8  mA                      | -40°C to 125°C |      | •    | 0.4  | V                  |

<sup>†</sup> CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to Co.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

# TPS7333Q electrical characteristics at I $_{O}$ = 10 mA, V $_{I}$ = 4.3 V, $\overline{EN}$ = 0 V, C $_{O}$ = 4.7 $\mu\text{F}$ (CSR $^{\dagger}$ = 1 $\Omega$ ), SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                      | TEST CO                                                   | NDITIONS <sup>‡</sup>                                                                   | TJ                                                                                                                                               | MIN   | TYP  | MAX   | UNIT   |

|--------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

| Outrot walta na                |                                                           |                                                                                         | 25°C                                                                                                                                             |       | 3.3  |       | V      |

| Output voltage                 | $4.3 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V},$ | $5 \text{ mA} \le I_{O} \le 500 \text{ mA}$                                             | -40°C to 125°C                                                                                                                                   | 3.23  |      | 3.37  | V      |

|                                | 10 mA                                                     | V. 2.22.V                                                                               | 25°C                                                                                                                                             |       | 4.5  | 7     |        |

|                                | $I_O = 10 \text{ mA},$                                    | V <sub>I</sub> = 3.23 V                                                                 | -40°C to 125°C                                                                                                                                   |       |      | 8     |        |

| Description                    | In - 100 mA                                               | V. – 2 22 V                                                                             | 25°C                                                                                                                                             |       | 44   | 60    | mV     |

| Dropout voltage                | $I_O = 100 \text{ mA},$                                   | V <sub>I</sub> = 3.23 V                                                                 | -40°C to 125°C                                                                                                                                   |       |      | 80    | IIIV   |

|                                | IO = 500 mA,                                              | V <sub>I</sub> = 3.23 V                                                                 | 25°C                                                                                                                                             |       | 235  | 300   |        |

|                                | IQ = 500 IIIA,                                            | V  = 3.23 V                                                                             | -40°C to 125°C                                                                                                                                   |       |      | 400   |        |

| Pass-element series resistance | (3.23 V – V <sub>O</sub> )/I <sub>O</sub> ,               | V <sub>I</sub> = 3.23 V,                                                                | 25°C                                                                                                                                             |       | 0.44 | 0.6   | Ω      |

| Pass-element series resistance | I <sub>O</sub> = 500 mA                                   | •                                                                                       | -40°C to 125°C                                                                                                                                   |       |      | 0.8   | 32     |

| lanut va quilatian             | V: 42 V to 40 V                                           | 50 A < la < 500 mA                                                                      | 25°C                                                                                                                                             |       | 6    | 23    | mV     |

| Input regulation               | $V_{I} = 4.3 \text{ V to } 10 \text{ V},$                 | $50 \mu\text{A} \le I_{O} \le 500 \text{mA}$                                            | -40°C to 125°C                                                                                                                                   |       |      | 29    | IIIV   |

|                                | I <sub>O</sub> = 5 mA to 500 mA                           | 421/21/2101/                                                                            | 25°C                                                                                                                                             |       | 21   | 38    | mV     |

| Output regulation              | 10 = 2 HIM 10 200 HIM                                     | $  4.3 \text{ V} \leq \text{V}   \leq 10 \text{ V}$                                     | -40°C to 125°C                                                                                                                                   |       |      | 75    | IIIV   |

|                                | lo - 50 uA to 500 m/                                      | $I_{O} = 50 \mu A \text{ to } 500 \text{ mA}, 4.3 \text{ V} \le V_{I} \le 10 \text{ V}$ |                                                                                                                                                  |       | 31   | 60    | mV     |

|                                | ΙΟ = 50 μΑ (0 500 ΠΙΑ                                     | $A, 4.5 \lor 5 \lor   5 \lor 0 \lor$                                                    | -40°C to 125°C                                                                                                                                   |       |      | 120 m | IIIV   |

|                                |                                                           | ΙΟ = 50 μΑ                                                                              | 25°C                                                                                                                                             | 43    | 51   |       |        |

| Ripple rejection               | f = 120 Hz                                                | ΙΟ = 50 μΑ                                                                              | A -40°C to 125°C 29  25°C 21 38  -40°C to 125°C 75  25°C 31 60  -40°C to 125°C 120  25°C 43 51  -40°C to 125°C 40  25°C 39 49  -40°C to 125°C 36 |       |      | dB    |        |

| Rippie rejection               | T = 120 HZ                                                | IO = 500 mA                                                                             | 25°C                                                                                                                                             | 39    | 49   |       | uБ     |

|                                |                                                           | IQ = 500 IIIA                                                                           | -40°C to 125°C                                                                                                                                   | 36    |      |       |        |

| Output noise-spectral density  | f = 120 Hz                                                |                                                                                         | 25°C                                                                                                                                             |       | 2    |       | μV/√Hz |

|                                |                                                           | $C_0 = 4.7  \mu F$                                                                      | 25°C                                                                                                                                             |       | 274  |       |        |

| Output noise voltage           | 10 Hz ≤ f ≤ 100 kHz                                       | C <sub>O</sub> = 10 μF                                                                  | 25°C                                                                                                                                             |       | 228  |       | μVrms  |

|                                |                                                           | C <sub>O</sub> = 100 μF                                                                 | 25°C                                                                                                                                             |       | 159  |       |        |

| RESET trip-threshold voltage   | V <sub>O</sub> decreasing                                 |                                                                                         | -40°C to 125°C                                                                                                                                   | 2.868 |      |       | V      |

| RESET hysteresis voltage       |                                                           |                                                                                         | 25°C                                                                                                                                             |       | 18   |       | mV     |

| RESET output low voltage       | V. 20V                                                    |                                                                                         | 25°C                                                                                                                                             |       | 0.17 | 0.4   |        |

| KESET output low voitage       | V <sub>I</sub> = 2.8 V,                                   | IO(RESET) = -1 mA                                                                       | -40°C to 125°C                                                                                                                                   |       |      | 0.4   | V      |

<sup>†</sup>CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>O</sub>.

<sup>&</sup>lt;sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

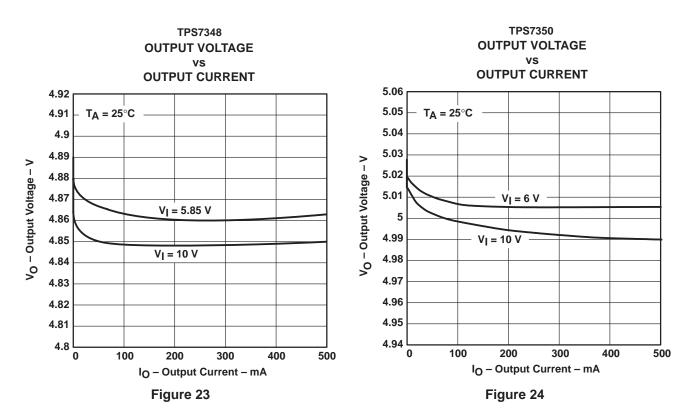

# TPS7348Q electrical characteristics at I<sub>O</sub> = 10 mA, V<sub>I</sub> = 5.85 V, $\overline{\text{EN}}$ = 0 V, C<sub>O</sub> = 4.7 $\mu\text{F}$ (CSR<sup>†</sup> = 1 $\Omega$ ), SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                      | TEST CO                                                                              | NDITIONS <sup>‡</sup>                     | TJ             | MIN  | TYP  | MAX       | UNIT   |

|--------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|----------------|------|------|-----------|--------|

| Output voltogo                 |                                                                                      |                                           | 25°C           |      | 4.85 |           | V      |

| Output voltage                 | $5.85 \text{ V} \le \text{V}_{I} \le 10 \text{ V},$                                  | $5 \text{ mA} \le I_O \le 500 \text{ mA}$ | -40°C to 125°C | 4.75 |      | 4.95      | V      |

|                                | I <sub>O</sub> = 10 mA,                                                              | V <sub>I</sub> = 4.75 V                   | 25°C           |      | 2.9  | 6         |        |

|                                | 10 = 10 111A,                                                                        | V   = 4.75 V                              | -40°C to 125°C |      |      | 8         |        |

| Dropout voltage                | I <sub>O</sub> = 100 mA,                                                             | V <sub>I</sub> = 4.75 V                   | 25°C           |      | 28   | 37        | m∨     |

| Dropout voltage                | 10 = 100 mz,                                                                         | V   = 4.75 V                              | -40°C to 125°C |      |      | 54        | 111 V  |

|                                | I <sub>O</sub> = 500 mA,                                                             | V <sub>I</sub> = 4.75 V                   | 25°C           |      | 150  | 180       |        |

|                                | 10 = 300 IIIA,                                                                       | V  = 4.75 V                               | -40°C to 125°C |      |      | 250       |        |

| Pass-element series resistance | (4.75 V – V <sub>O</sub> )/I <sub>O</sub> ,                                          | V <sub>I</sub> = 4.75 V,                  | 25°C           |      | 0.28 | 0.37      | Ω      |

| Pass-element series resistance | $I_{O} = 500 \text{ mA}$                                                             |                                           | -40°C to 125°C |      |      | 0.52      | 22     |

| Input regulation               | \/\. = 5.95.\/ to 10.\/                                                              | 50 μA ≤ I <sub>O</sub> ≤ 500 mA           | 25°C           |      | 9    | 35        | mV     |

| Imput regulation               | V  = 5.65 V to 10 V,                                                                 | 50 μA ≤ 1O ≤ 500 IIIA                     | -40°C to 125°C |      |      | 37        | IIIV   |

|                                | I <sub>O</sub> = 5 mA to 500 mA                                                      | 5 95 V < V, < 10 V                        | 25°C           |      | 28   | 42        | mV     |

| Output regulation              | 10 = 3 IIIA to 300 IIIA                                                              | , 5.85 V \(\sigma\) \(\sigma\)            | -40°C to 125°C |      | 80   |           | IIIV   |

|                                | $I_O = 50 \mu A \text{ to } 500 \text{ mA}, 5.85 \text{ V} \le V_I \le 10 \text{ V}$ |                                           | 25°C           |      | 42   | 65        | mV     |

|                                | ΙΟ = 30 μΑ 10 300 ΠΙΑ                                                                | x, 5.85 v ≤ v  ≤ 10 v                     | -40°C to 125°C |      |      | 65<br>130 | IIIV   |

|                                |                                                                                      | ΙΟ = 50 μΑ                                | 25°C           | 42   | 53   |           |        |

| Ripple rejection               | f = 120 Hz                                                                           | 10 = 30 μΑ                                | -40°C to 125°C | 39   |      |           | dB     |

| Rippie rejection               | 1 = 120112                                                                           | I <sub>O</sub> = 500 mA                   | 25°C           | 39   | 50   |           | uБ     |

|                                |                                                                                      | IQ = 300 IIIA                             | -40°C to 125°C | 35   |      |           |        |

| Output noise-spectral density  | f = 120 Hz                                                                           |                                           | 25°C           |      | 2    |           | μV/√Hz |

|                                |                                                                                      | $C_0 = 4.7  \mu F$                        | 25°C           |      | 410  |           |        |

| Output noise voltage           | 10 Hz ≤ f ≤ 100 kHz                                                                  | C <sub>O</sub> = 10 μF                    | 25°C           |      | 328  |           | μVrms  |

|                                |                                                                                      | C <sub>O</sub> = 100 μF                   | 25°C           |      | 212  |           |        |

| RESET trip-threshold voltage   | V <sub>O</sub> decreasing                                                            |                                           | -40°C to 125°C | 4.5  |      | 4.7       | V      |

| RESET hysteresis voltage       |                                                                                      |                                           | 25°C           |      | 26   |           | mV     |

| DECET cutput lovu valtage      | 1                                                                                    | 25°C                                      |                |      | 0.2  | 0.4       |        |

| RESET output low voltage       | IO(RESET) = -1.2  m                                                                  | A, V   = 4.12 V                           | -40°C to 125°C |      |      | 0.4       | V      |

<sup>†</sup> CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>0</sub>.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

# TPS7350Q electrical characteristics at I $_{O}$ = 10 mA, V $_{I}$ = 6 V, $\overline{EN}$ = 0 V, C $_{O}$ = 4.7 $\mu\text{F}$ (CSR $^{\dagger}$ = 1 $\Omega$ ), SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                      | TEST CON                                         | IDITIONS <sup>‡</sup>                     | TJ             | MIN  | TYP  | MAX  | UNIT               |  |

|--------------------------------|--------------------------------------------------|-------------------------------------------|----------------|------|------|------|--------------------|--|

| Output valtage                 |                                                  |                                           | 25°C           |      | 5    |      | V                  |  |

| Output voltage                 | $6 \text{ V} \le \text{V}_{I} \le 10 \text{ V},$ | $5 \text{ mA} \le I_O \le 500 \text{ mA}$ | -40°C to 125°C | 4.9  |      | 5.1  | l                  |  |

|                                | 1- 10 mA                                         | \/. 4.00.\/                               | 25°C           |      | 2.9  | 6    |                    |  |

|                                | $I_{O} = 10 \text{ mA},$                         | V <sub>I</sub> = 4.88 V                   | -40°C to 125°C |      |      | 8    |                    |  |

| Description                    | IO = 100 mA,                                     | V <sub>I</sub> = 4.88 V                   | 25°C           |      | 27   | 35   | mV                 |  |

| Dropout voltage                | 10 = 100 mA,                                     | V = 4.00 V                                | -40°C to 125°C |      |      | 50   | 1117               |  |

|                                | Io = 500 mA                                      | V <sub>I</sub> = 4.88 V                   | 25°C           |      | 146  | 170  |                    |  |

|                                | $I_{O} = 500 \text{ mA},$                        | V  = 4.00 V                               | -40°C to 125°C |      |      | 230  |                    |  |

| Pass-element series resistance | (4.88 V – V <sub>O</sub> )/I <sub>O</sub> ,      | V <sub>I</sub> = 4.88 V,                  | 25°C           |      | 0.27 | 0.35 | Ω                  |  |

| Pass-element series resistance | $I_{O} = 500 \text{ mA}$                         |                                           | -40°C to 125°C |      |      | 0.5  | 52                 |  |

| Input regulation               | V <sub>I</sub> = 6 V to 10 V,                    | $50  \mu A \le I_O \le 500  mA$           | 25°C           |      | 4    | 25   | mV                 |  |

| Input regulation               | V = 6 V 10 10 V,                                 | 20 μA ≥ 1O ≥ 200 IIIA                     | -40°C to 125°C |      |      | 45   | IIIV               |  |

|                                | $I_{O} = 5 \text{ mA to } 500 \text{ mA},$       | 6 \/ < \/ < 10 \/                         | 25°C           |      | 30   | 45   | mV                 |  |

| Output regulation              | 10 = 3 mA to 300 mA,                             | 0 v ≥ v  ≥ 10 v                           | -40°C to 125°C |      |      | 86   | IIIV               |  |

|                                | lo - 50 u \ to 500 m \                           | A, 6 V ≤ V <sub>I</sub> ≤ 10 V            | 25°C           |      | 45   | 65   | mV                 |  |

|                                | ΙΟ = 50 μΑ το 500 ΠΑ,                            | 0 v ≥ v  ≥ 10 v                           | -40°C to 125°C |      |      | 140  | IIIV               |  |

|                                |                                                  | ΙΟ = 50 μΑ                                | 25°C           | 43   | 53   |      |                    |  |

| Pinnla raigation               | f = 120 Hz                                       | ΙΟ = 50 μΑ                                | -40°C to 125°C | 38   |      |      | dB                 |  |

| Ripple rejection               | 1 = 120 HZ                                       | IO = 500 mA                               | 25°C           | 41   | 51   |      | uБ                 |  |

|                                |                                                  | IQ = 200 IIIA                             | -40°C to 125°C | 36   |      |      |                    |  |

| Output noise-spectral density  | f = 120 Hz                                       |                                           | 25°C           |      | 2    |      | μV/√ <del>Hz</del> |  |

|                                |                                                  | $C_0 = 4.7  \mu F$                        | 25°C           |      | 430  |      |                    |  |

| Output noise voltage           | 10 Hz ≤ f ≤ 100 kHz                              | C <sub>O</sub> = 10 μF                    | 25°C           |      | 345  |      | μVrms              |  |

|                                |                                                  | C <sub>O</sub> = 100 μF                   | 25°C           |      | 220  |      |                    |  |

| RESET trip-threshold voltage   | V <sub>O</sub> decreasing                        | -                                         | -40°C to 125°C | 4.55 |      | 4.75 | V                  |  |

| RESET hysteresis voltage       |                                                  |                                           | 25°C           |      | 28   |      | mV                 |  |

| DECET autout laurualta aa      |                                                  | V 405.V                                   | 25°C           |      | 0.15 | 0.4  | .,                 |  |

| RESET output low voltage       | IO(RESET) = -1.2  mA                             | , V  = 4.25 V                             | -40°C to 125°C |      |      | 0.4  | V                  |  |

<sup>†</sup> CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>0</sub>.

<sup>&</sup>lt;sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

### switching characteristics

| PARAMETER            | TEST CONDITIONS |      | TPS7301<br>TPS7348 | ,   |     | UNIT |

|----------------------|-----------------|------|--------------------|-----|-----|------|

|                      |                 |      | MIN                | TYP | MAX |      |

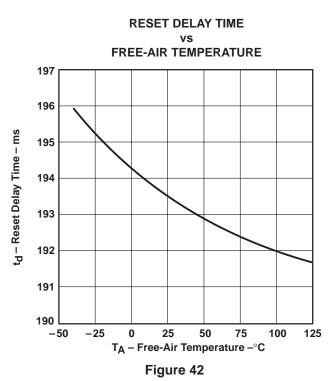

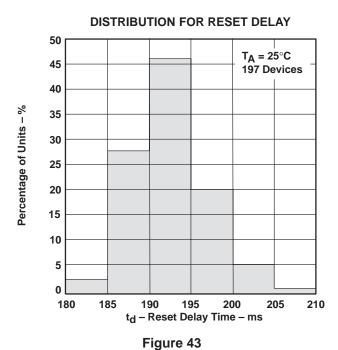

| DESET time out delay | Coo Figure F    | 25°C | 140                | 200 | 260 |      |

| RESET time-out delay | See Figure 5    |      | 100                |     | 300 | ms   |

## electrical characteristics at I $_{O}$ = 10 mA, $\overline{EN}$ = 0 V, C $_{O}$ = 4.7 $\mu F$ (CSR $^{\dagger}$ = 1 $\Omega$ ), T $_{J}$ = 25°C, SENSE/FB shorted to OUT (unless otherwise noted)

| PARAMETER                                      | TEST CON                                                                                       | TEST CONDITIONS <sup>‡</sup>                             |     |       | TPS7301Y, TPS7333Y<br>TPS7348Y, TPS7350Y |    |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-------|------------------------------------------|----|--|

|                                                |                                                                                                |                                                          | MIN | TYP   | MAX                                      |    |  |

| Ground current (active mode)                   | $\overline{\text{EN}} \le 0.5 \text{ V},$<br>0 mA $\le \text{I}_{\text{O}} \le 500 \text{ mA}$ | $V_I = V_O + 1 V$ ,                                      |     | 340   |                                          | μА |  |

| Input current (standby mode)                   | $\overline{EN} = V_{I},$                                                                       | $2.7~\text{V} \leq \text{V}_{\text{I}} \leq 10~\text{V}$ |     | 0.01  |                                          | μΑ |  |

| Output current limit                           | $V_0 = 0 V$ ,                                                                                  | V <sub>I</sub> = 10 V                                    |     | 1.2   |                                          | Α  |  |

| Pass-element leakage current in standby mode   | $\overline{EN} = V_{I},$                                                                       | $2.7~V \leq V_{\mbox{\scriptsize I}} \leq 10~V$          |     | 0.01  |                                          | μΑ |  |

| RESET leakage current                          | Normal operation,                                                                              | V at RESET = 10 V                                        |     | 0.02  |                                          | μΑ |  |

| Thermal shutdown junction temperature          |                                                                                                |                                                          |     | 165   |                                          | °C |  |

| EN logic low (active mode)                     | $2.7 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V}$                                       |                                                          |     |       | 0.5                                      | V  |  |

| EN hysteresis voltage                          |                                                                                                |                                                          |     | 50    |                                          | mV |  |

| EN input current                               | 0 V ≤ V <sub>I</sub> ≤ 10 V                                                                    |                                                          |     | 0.001 |                                          | μΑ |  |

| Minimum V <sub>I</sub> for active pass element |                                                                                                |                                                          |     | 2.05  |                                          | V  |  |

| Minimum V <sub>I</sub> for valid RESET         | $IO(RESET) = -300 \mu$                                                                         | A                                                        |     | 1     | ·                                        | V  |  |

<sup>†</sup> CSR (compensation series resistance) refers to the total series resistance, including the equivalent series resistance (ESR) of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>0</sub>.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

SLVS124F - JUNE 1995 - REVISED JANUARY 1999

## TPS7301Y electrical characteristics at I<sub>O</sub> = 10 mA, V<sub>I</sub> = 3.5 V, $\overline{\text{EN}}$ = 0 V, C<sub>O</sub> = 4.7 $\mu\text{F}$ (CSR<sup>†</sup> = 1 $\Omega$ ), T<sub>J</sub> = 25°C, FB shorted to OUT at device leads (unless otherwise noted)

| PARAMETER                                   | TEST CO                                                                 | ONDITIONS <sup>‡</sup>                                  | MIN TYP | MAX | UNIT   |

|---------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|---------|-----|--------|

| Reference voltage (measured at FB)          |                                                                         |                                                         | 1.182   |     | V      |

|                                             | V <sub>I</sub> = 2.4 V,                                                 | $50 \ \mu\text{A} \le I_{\mbox{O}} \le 150 \ \mbox{mA}$ | 0.7     |     |        |

|                                             | V <sub>I</sub> = 2.4 V,                                                 | $150~\text{mA} \leq I_{\mbox{O}} \leq 500~\text{mA}$    | 0.83    |     |        |

| Pass-element series resistance (See Note 2) | V <sub>I</sub> = 2.9 V,                                                 | $50 \ \mu A \le I_O \le 500 \ mA$                       | 0.52    |     | Ω      |

|                                             | V <sub>I</sub> = 3.9 V,                                                 | $50 \ \mu\text{A} \le I_{\mbox{O}} \le 500 \ \mbox{mA}$ | 0.32    |     |        |

|                                             | V <sub>I</sub> = 5.9 V,                                                 | $50 \ \mu\text{A} \le I_{\mbox{O}} \le 500 \ \mbox{mA}$ | 0.23    |     |        |

| Input regulation                            | V <sub>I</sub> = 2.5 V to 10 V,<br>See Note 1                           | $50 \mu A \le I_O \le 500 \text{ mA},$                  | 3       |     | mV     |

| Outroit no miletion                         | $2.5 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V},$<br>See Note 1 | $I_O = 5$ mA to 500 mA,                                 | 5       |     | mV     |

| Output regulation                           | $2.5 \text{ V} \le \text{V}_{\text{I}} \le 10 \text{ V},$<br>See Note 1 | $I_O = 50 \mu\text{A} \text{ to } 500 \text{mA},$       | 7       |     | mV     |

|                                             |                                                                         | ΙΟ = 50 μΑ                                              | 59      |     |        |

| Ripple rejection                            | f = 120 Hz                                                              | I <sub>O</sub> = 500 mA,<br>See Note 1                  | 54      |     | dB     |

| Output noise-spectral density               | f = 120 Hz                                                              |                                                         | 2       |     | μV/√Hz |

|                                             |                                                                         | $C_0 = 4.7 \mu\text{F}$                                 | 95      |     |        |

| Output noise voltage                        | 10 Hz ≤ f ≤ 100 kHz                                                     | C <sub>O</sub> = 10 μF                                  | 89      |     | μVrms  |

|                                             |                                                                         | C <sub>O</sub> = 100 μF                                 | 74      |     |        |

| RESET hysteresis voltage§                   | Measured at VO(FB)                                                      |                                                         | 12      |     | mV     |

| RESET output low voltage§                   | V <sub>I</sub> = 2.13 V,                                                | I <sub>O</sub> (RESET) = 400 μA                         | 0.1     |     | V      |

| FB input current                            |                                                                         |                                                         | 0.1     |     | nA     |

<sup>†</sup> CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to Co.

To calculate dropout voltage, use equation: V<sub>DO</sub> = I<sub>O</sub> · r<sub>DS</sub>(on) r<sub>DS</sub>(on) is a function of both output current and input voltage. The parametric table lists r<sub>DS</sub>(on) for V<sub>I</sub> = 2.4 V, 2.9 V, 3.9 V, and 5.9 V, which corresponds to dropout conditions for programmed output voltages of 2.5 V, 3 V, 4 V, and 6 V respectively. For other programmed values, refer to Figure 33.

<sup>‡</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects must be taken into account separately.

<sup>§</sup> Output voltage programmed to 2.5 V with closed-loop configuration (see application information).

NOTES: 1. When V<sub>I</sub> < 2.9 V and I<sub>O</sub> > 150 mA simultaneously, pass element r<sub>DS(On)</sub> increases (see Figure 33) to a point where the resulting dropout voltage prevents the regulator from maintaining the specified tolerance range.

SLVS124F – JUNE 1995 – REVISED JANUARY 1999

## TPS7325Y electrical characteristics at I<sub>O</sub> = 10 mA, V<sub>I</sub> = 3.5 V, $\overline{\text{EN}}$ = 0 V, C<sub>O</sub> = 10 $\mu\text{F}$ (CSR<sup>†</sup> = 1 $\Omega$ ), T<sub>J</sub> = 25°C, SENSE shorted to OUT (unless otherwise noted)

| PARAMETER                       | TEST COI                                                               | TEST CONDITIONS <sup>‡</sup>                         |      | MAX | UNIT               |

|---------------------------------|------------------------------------------------------------------------|------------------------------------------------------|------|-----|--------------------|